3.2典型组合逻辑部件设计

1.译码器和编码器

译码器

- 一种多输入、多输出的组合电路

- 电路功能反映输入编码与输出编码之间的映射关系

- 最简单的译码器(译码器)输入和输出关系是:输入的二进制编码值是x,则第x条输出线为1,其余输出全为0

- 可以通过使能端EN来控制

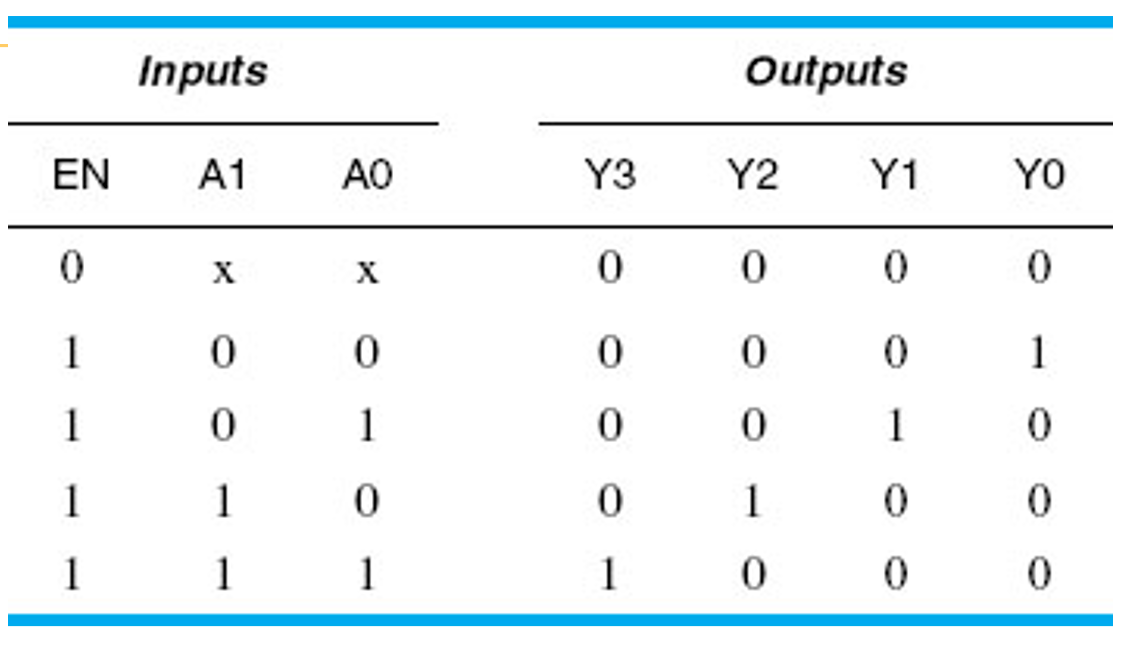

2-4译码器74X139

- 输出端高电平有效,表示选中对应输入信号的最小项

- 通过使能端EN禁止或实现相应的功能

- EN=0时,输出为全0

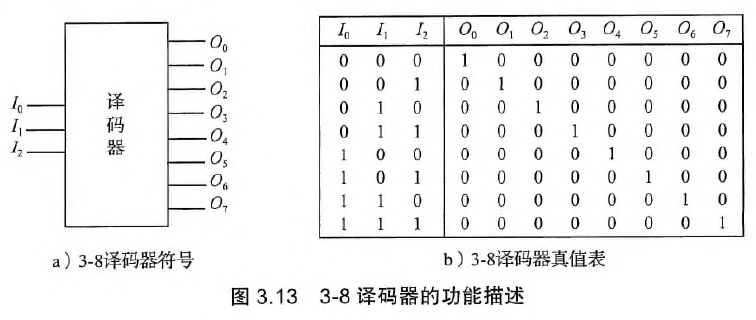

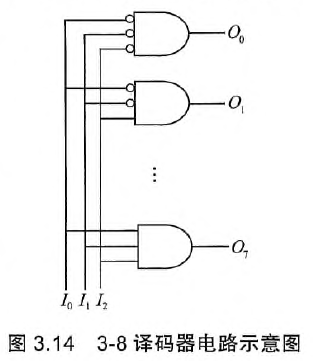

3-8译码器

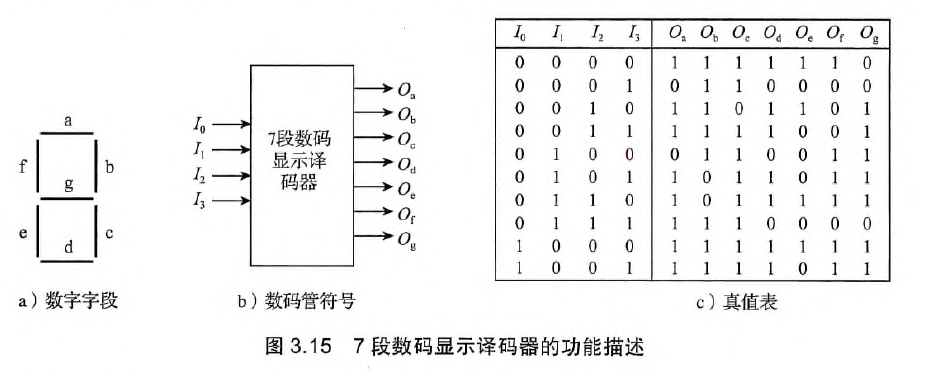

七段显示译码器

编码器

- 译码器的反函数电路

- 最常见:编码器(二进制编码器)

- 个输入端

- n个输出端

- 分类

- 互斥(唯一输入)编码器

- 优先级编码器

- 最常见:编码器(二进制编码器)

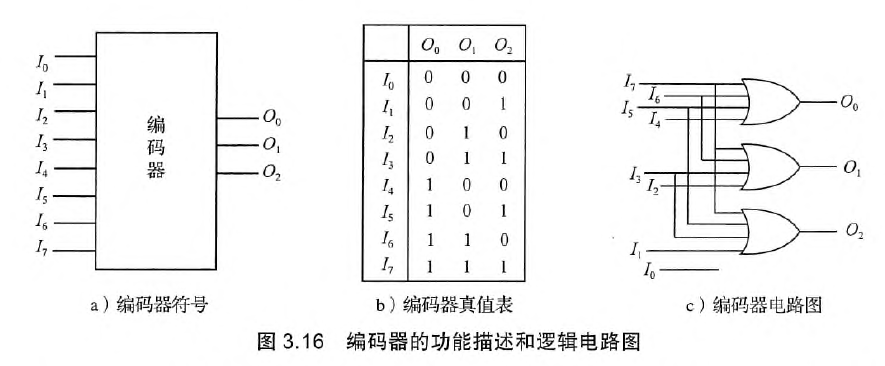

8-3编码器(互斥编码器)

- 是一组互斥变量,每次只有一个输入端是1,其余都为0,输出为i的二进制编码

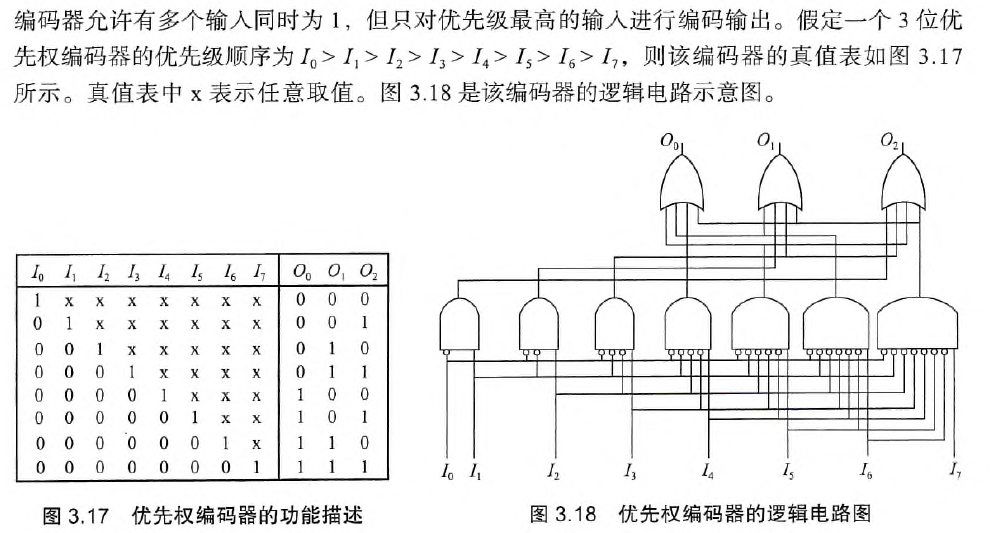

优先权编码器

多个输入可同时为1,但只对优先级最高的输入进项编码输出

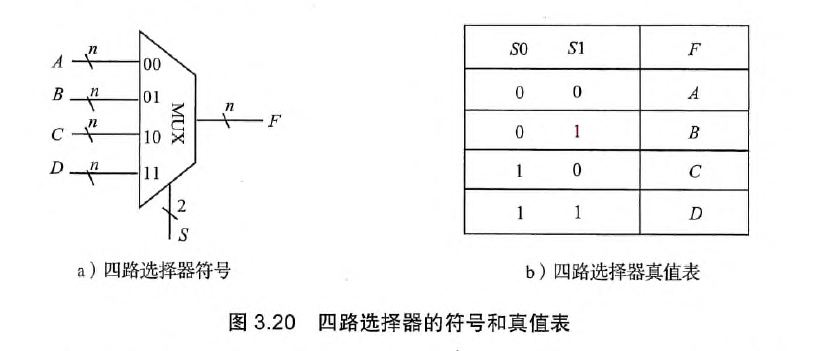

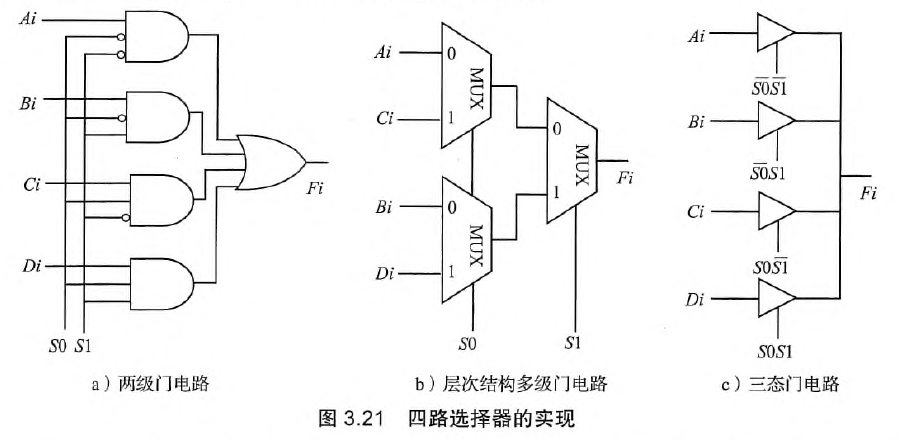

2.多路选择器和多路分配器

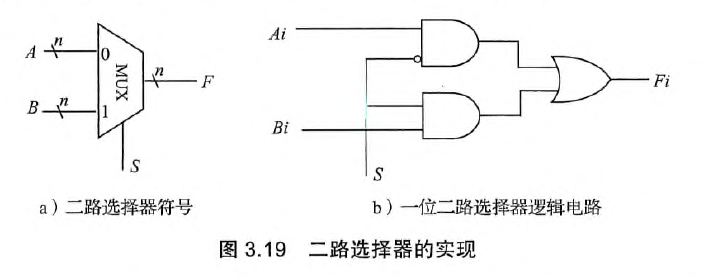

多路选择器

2-路选择器有两个输入端和一个输出端,有一个控制端,用于控制选择哪一路输出

每个输入、输出通常都有n位

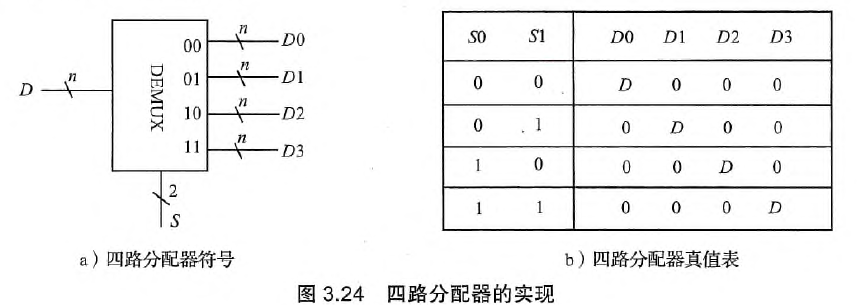

多路分配器

把唯一的输入信号发送到多个输出端中的一个

从哪一个输出端送出信号,取决于控制端

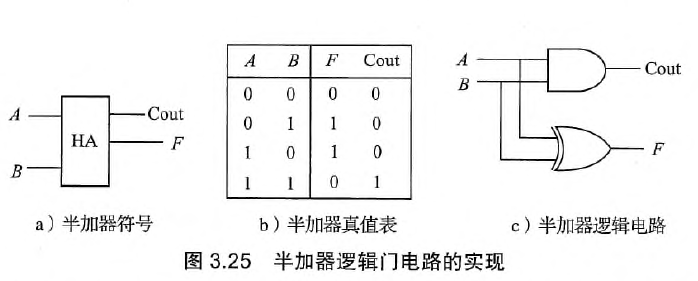

3.半加器和全加器

半加器(Half Adder, HA)

只考虑加数和被加数,不考虑低位来的进位

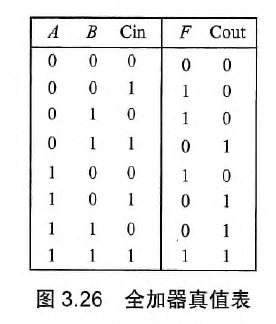

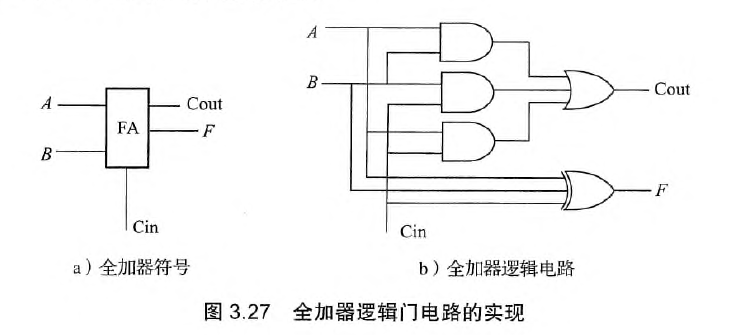

全加器(Full Adder, FA)

输入为加数、被加数和低位进位Cin,输出为和F、进位Cout

- Title: 3.2典型组合逻辑部件设计

- Author: SyEic_L

- Created at : 2025-03-10 17:13:56

- Updated at : 2025-03-11 22:07:58

- Link: https://blog.syeicl.vip/2025/03/10/3-2典型组合逻辑部件设计/

- License: This work is licensed under CC BY-NC-SA 4.0.

推荐阅读

Comments