3.3组合逻辑电路时序分析

1.传输延迟和最小延迟

用时序图反映电路的延迟

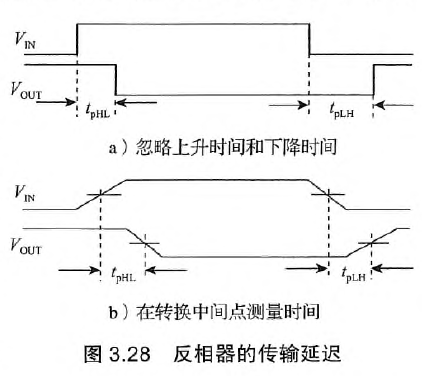

- 下降沿延迟:输入变化引起相应输出从高到低变化的时间

- 上升沿延迟:输入变化引起相应输出从低到高变化的时间

通常取信号转换时间中间点来测量延迟时间(以反相器电路为例)

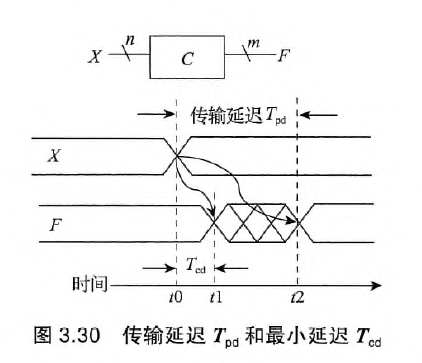

时序特征主要包括传输延迟和最小延迟

传输延迟Tpd:从输入端的变化开始到所有输出端得到最终稳定的信号的最长时间

最小时间Tcd:从输入端的变化开始到任何一个输出开始发生改变所需的最短时间

关键路径:一个组合逻辑电路在输入和输出之间经过的最长路径(最慢的)

传输延迟就是关键路径上所有元件的传输延迟之和

最小延迟就是最短路径上所有元件的最小延迟之和

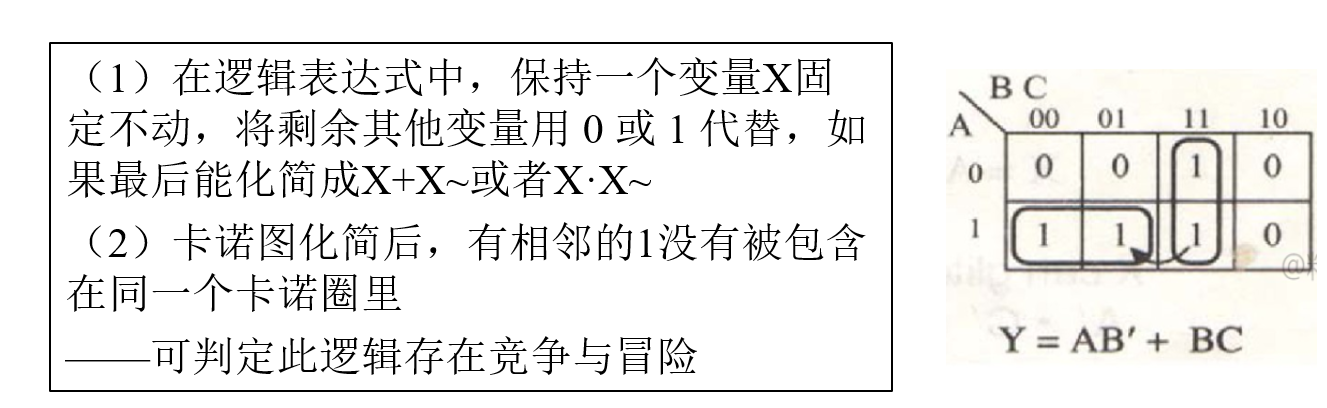

2.竞争冒险

竞争:某个输入信号经过两条或两条以上的不同路径作用到输出端,由于路径延迟不同,因而该输出信号对输出端会发生先后不同的影响,该现象称为竞争(race)

毛刺:由于竞争的存在,在输入信号变化的瞬间,输出端可能会出现不正确的尖峰信号,这种信号称为毛刺(glitch)

冒险:出现毛刺的电路称为存在冒险(hazard)

- Title: 3.3组合逻辑电路时序分析

- Author: SyEic_L

- Created at : 2025-03-14 20:37:42

- Updated at : 2025-03-14 20:37:42

- Link: https://blog.syeicl.vip/2025/03/14/3-3组合逻辑电路时序分析/

- License: This work is licensed under CC BY-NC-SA 4.0.

推荐阅读

Comments