4.1时序逻辑电路概述

时序逻辑:输出结果不仅取决于当前时刻的输入值,还取决于电路过去时刻的行为(当前状态、现态、旧状态)

- 电路中有存储元件,存储逻辑信号(0、1)的值

- 电路输入值发生变化时,新的输入值可能使得电路保持当前状态,也可能使得电路状态发生改变,进入新的状态。

1.时序逻辑与有限状态机

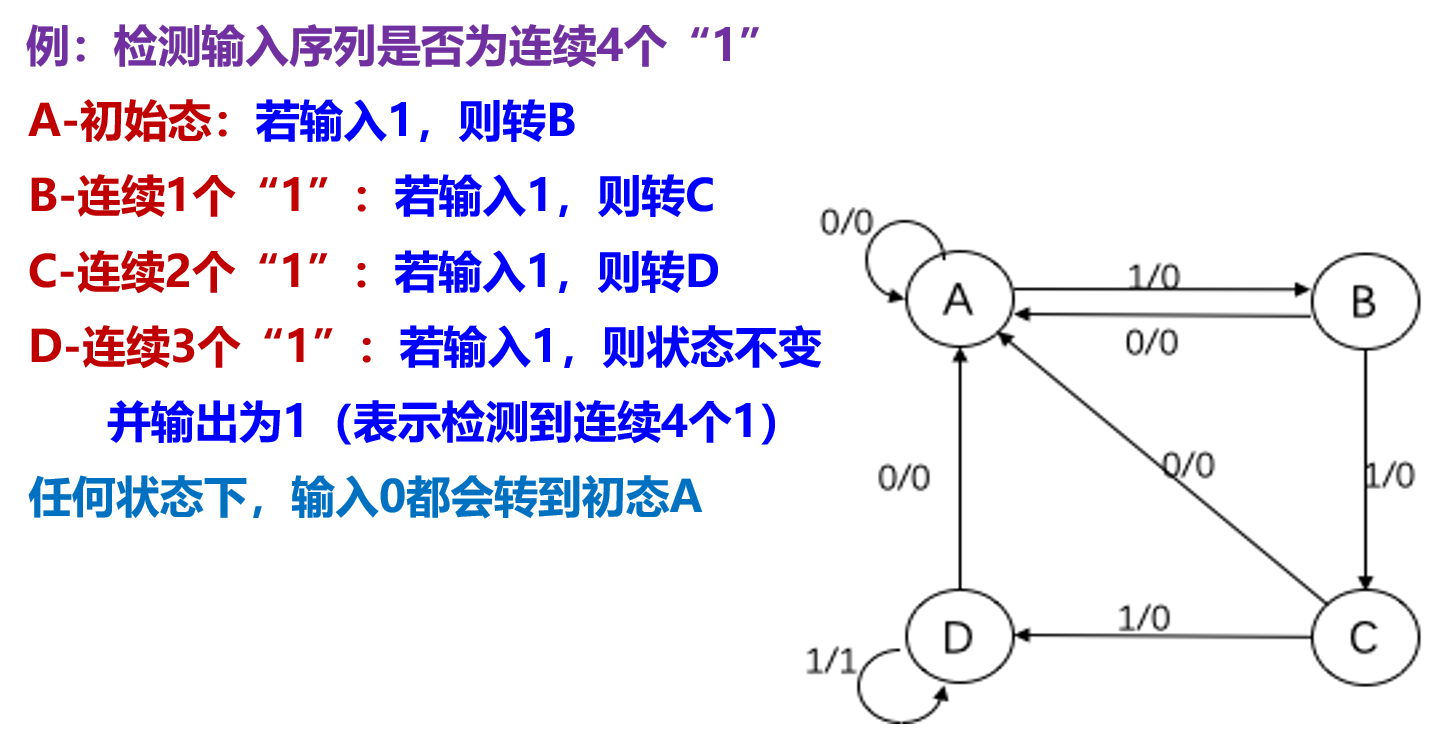

有限状态机是一种刻画状态以及状态转换的理论工具

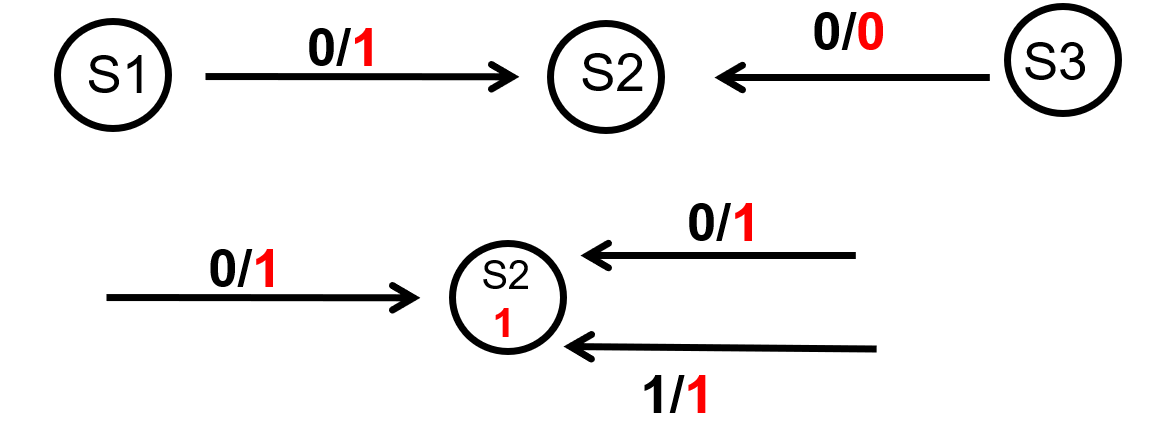

通常用状态图描述有限状态机

状态:用包含状态符号的圆圈表示

状态转换方向:用有向边表示,并在边上标注引起状态变换的输入信号值和相应输出(若输出只与当前状态有关,则可以把输出标注在状态圆圈中)

用数字逻辑实现一个有限状态机,需要:

- 把状态机的输入、输出以及内部状态都转换成二进制表示,这里的关键是状态的二进制编码

- 设计一种状态记忆电路(存储元件)。使用双稳态器件记忆状态,如SR锁存器,D触发器,JK触发器等

- 设计状态记忆电路的激励函数(根据当前输入把旧状态改为新状态的函数)和输出函数(根据旧状态和当前输入来改变电路输出结果的函数),并完成定时分析

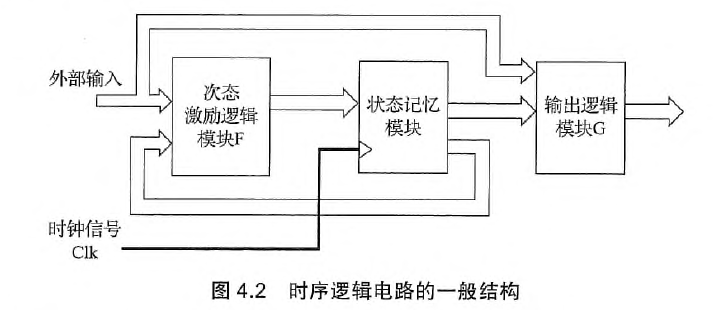

2.时序逻辑电路的基本结构

时序逻辑电路的一般结构:

状态记忆模块:有多个状态记忆单元构成(存储元件)

状态激励逻辑模块F:激励函数(现态和外部输入的逻辑函数)

输出逻辑模块G:输出函数(现态和外部输入的逻辑函数)

- Mealy型:输出依赖于当前状态和当前输入信号

- Moore型:输出仅依赖于当前状态,和当前输入无关

根据状态转换方式的不同有同步时序逻辑电路和异步时序逻辑电路

- 同步时序逻辑电路:在统一的时钟信号控制下进行状态转换

- 异步时序逻辑电路:没有统一的时钟信号来控制状态的改变

Clk:固定周期的标准脉冲信号

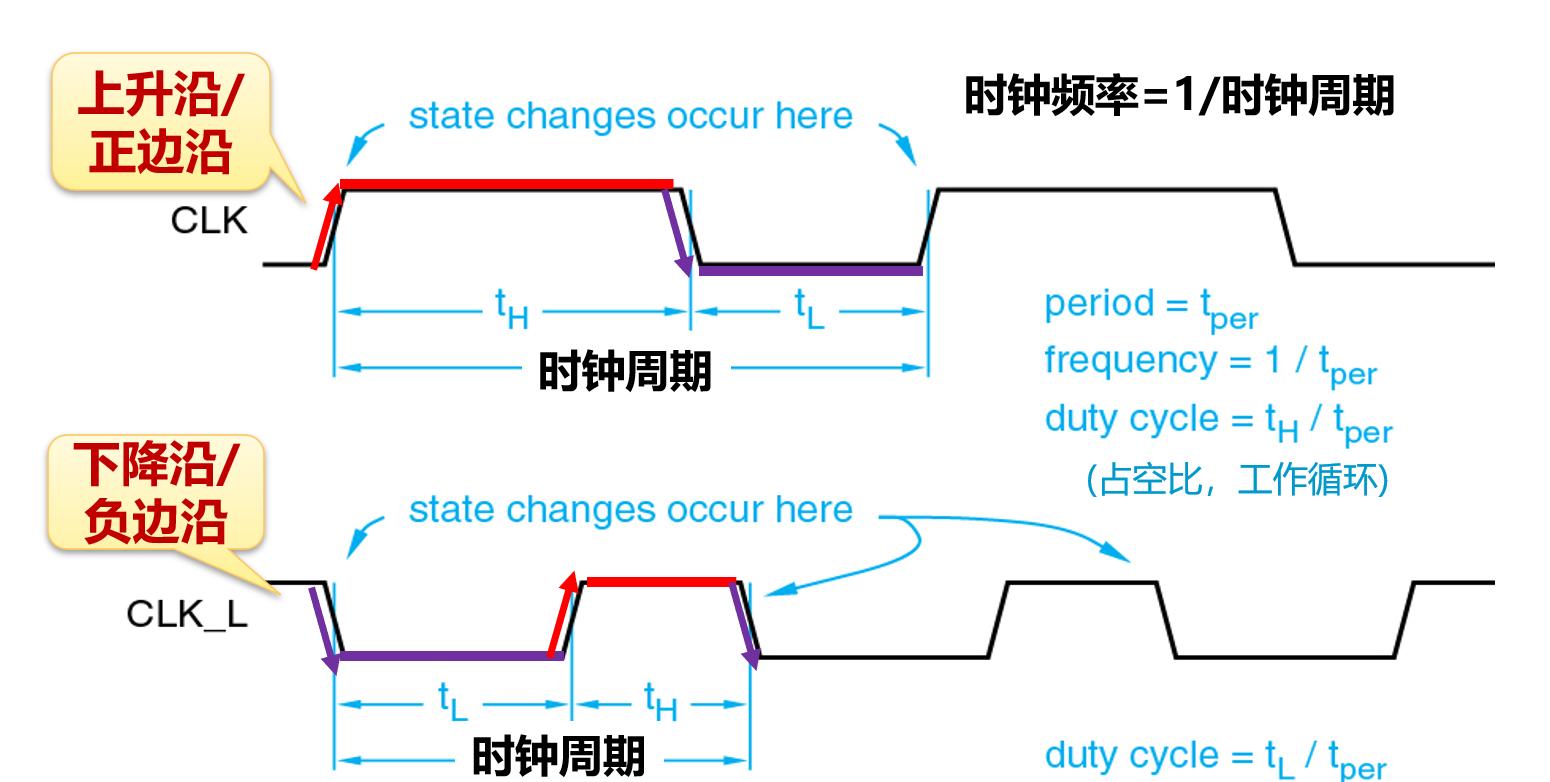

3.时序逻辑电路的定时

时钟脉冲

- 按一定电压幅度,按固定时间间隔,连续发出的脉冲信号

- 时钟脉冲之间的时间间隔称为时钟周期,单位是秒

- 1秒产生的脉冲个数称为时钟频率,单位是Hz

- 状态变换:电平触发或边沿出发

- 边沿触发方式分为上升沿触发和下降沿触发两种类型

- Title: 4.1时序逻辑电路概述

- Author: SyEic_L

- Created at : 2025-03-14 20:38:00

- Updated at : 2025-03-14 20:38:00

- Link: https://blog.syeicl.vip/2025/03/14/4-1时序逻辑电路概述/

- License: This work is licensed under CC BY-NC-SA 4.0.

推荐阅读

Comments