4.2锁存器和触发器

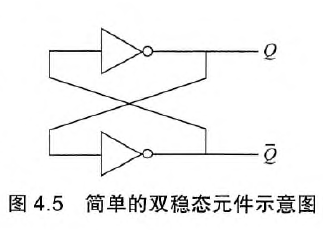

1.双稳态元件

用于存储1位二进制数据,有两个互补的输出状态

- 状态1:置位(Set)状态,表示存储逻辑“1”

- 状态0:复位(Reset)状态,表示存储逻辑“0”

双稳态元件的简单实现

串联两个反相器,则反相器的输出状态不同,且保持稳定

双稳态元件无法改变电路状态

用1个或多个输入信号能驱动双稳态元件进入稳定状态,这些输入信号称为激励信号或激励输入

根据触发方式不同,可以实现两种类型的存储元件:

- 锁存器

- 触发器

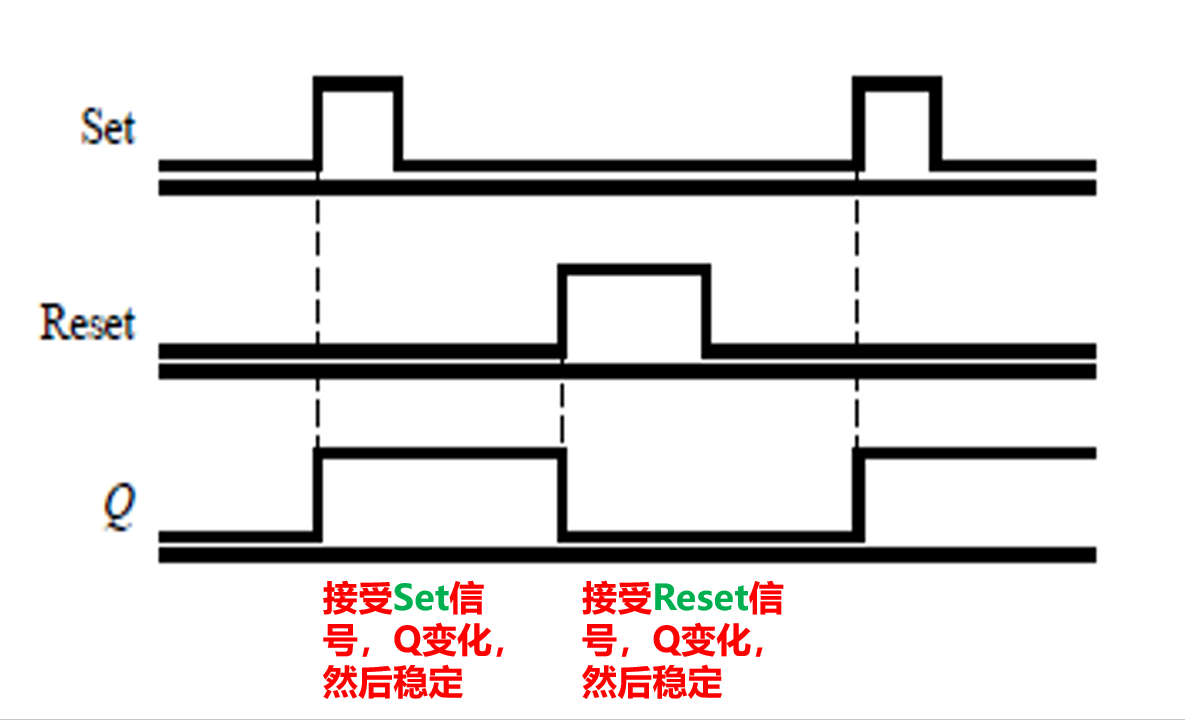

锁存器

通过激励输入的电平信号来控制存储元件的状态

置位复位锁存器:具有置位和复位激励信号

- 置位激励信号Set有效时:强制存储元件的输出Q为1

- 复位激励信号Reset有效时:强制存储元件的输出Q为0

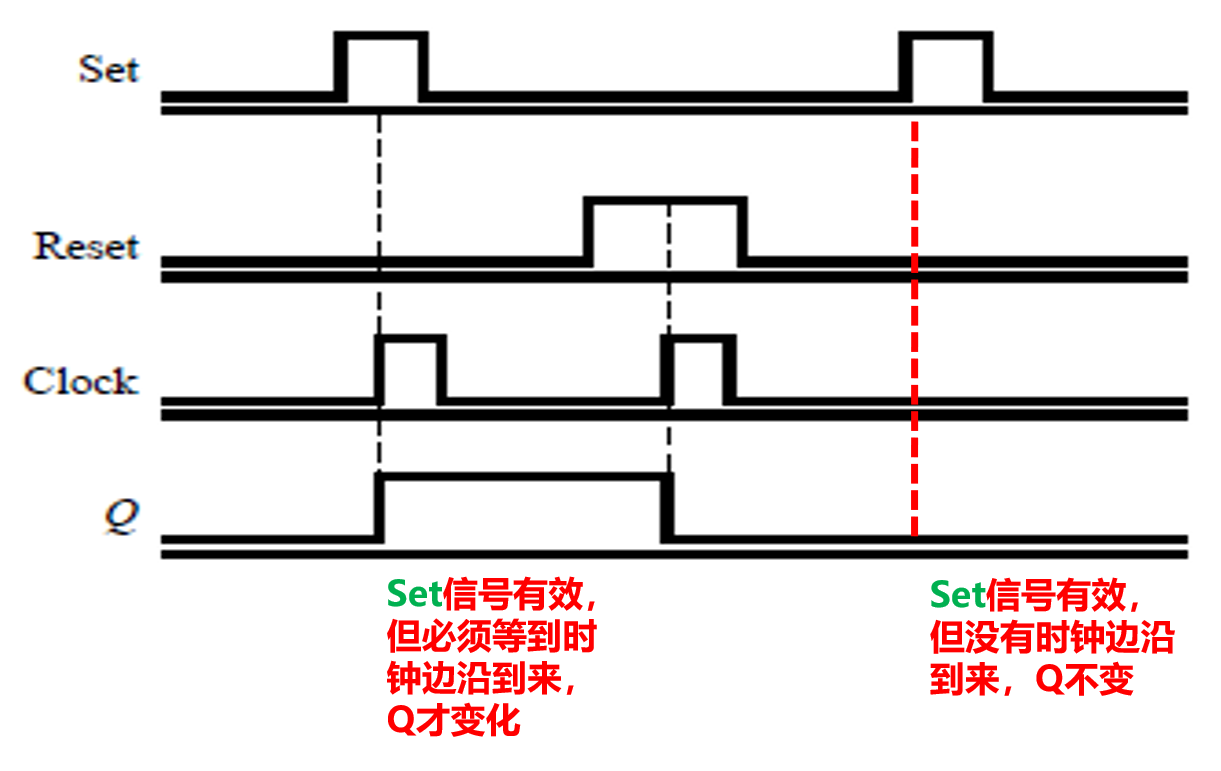

触发器

- 具有时钟控制信号

- 通过时钟信号的边沿来触发存储元件改变状态

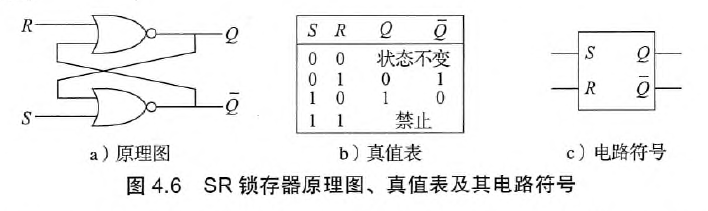

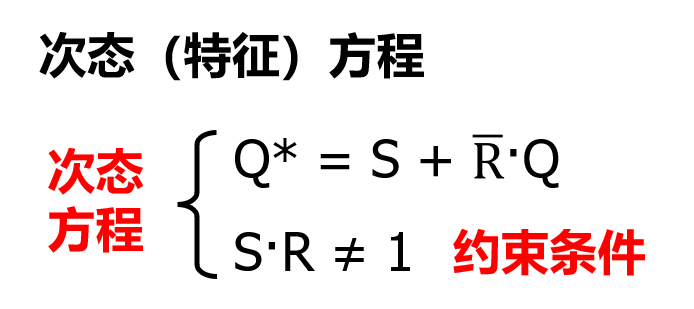

2.SR锁存器

使用一对交叉耦合的或非门构成双稳态电路,S为置位输入端,R是重置输入端

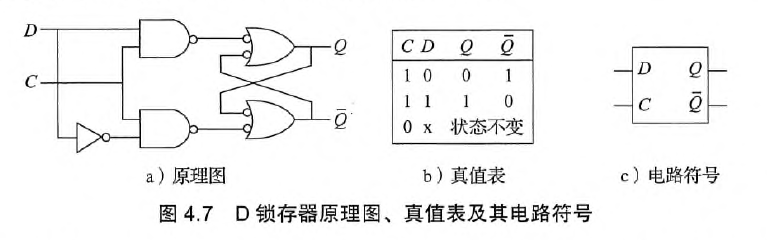

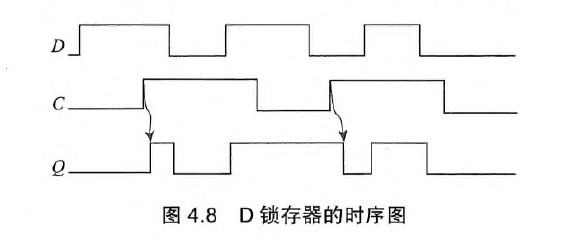

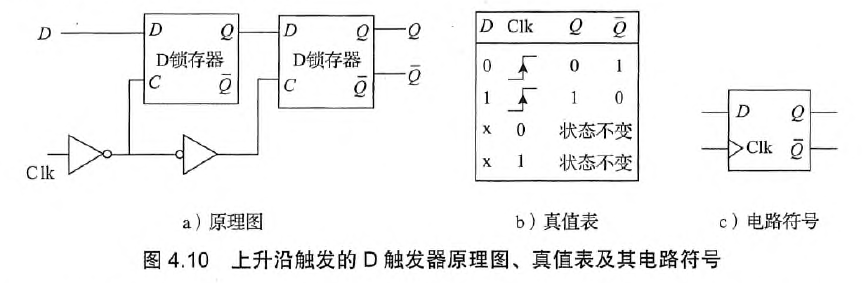

3.D锁存器

- 数据输入段:D

- 使能控制端:C

- C = 0时,电路状态保持不变

- C = 1时

- D = 1时,Q = 1

- D = 0时,Q = 0

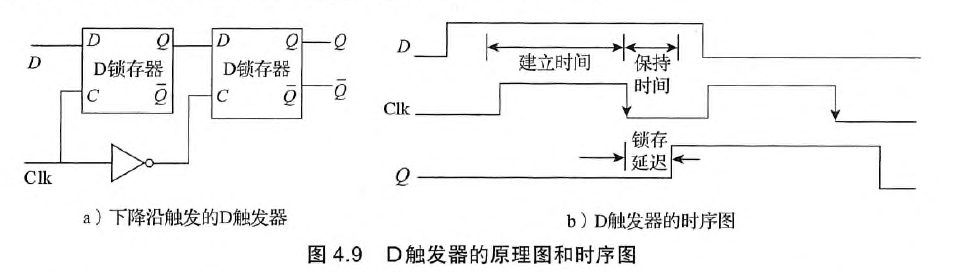

4.D触发器

- 由一对主、从D锁存器构成

从时钟触发边沿到来,到输出端Q改变为D值的时间称为锁存延迟,即CLK→Q时间,、 (从锁存器)

建立时间:输入信号D在时钟边沿到达前需稳定的时间 (主锁存器)

保持时间:输入信号D在时钟边沿到达后需继续稳定的时间

等从锁存器完成写入,避免主锁存器在上升沿过程中写入新的D值

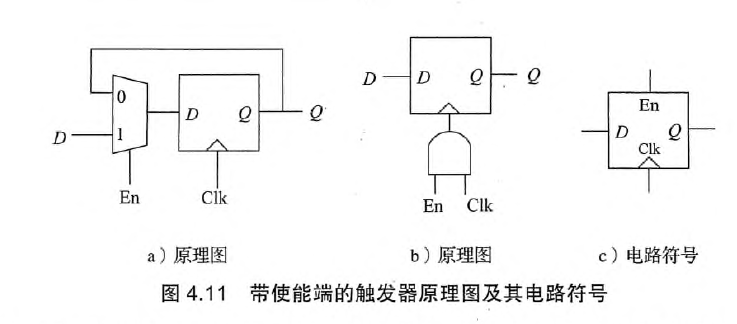

带使能端的D触发器

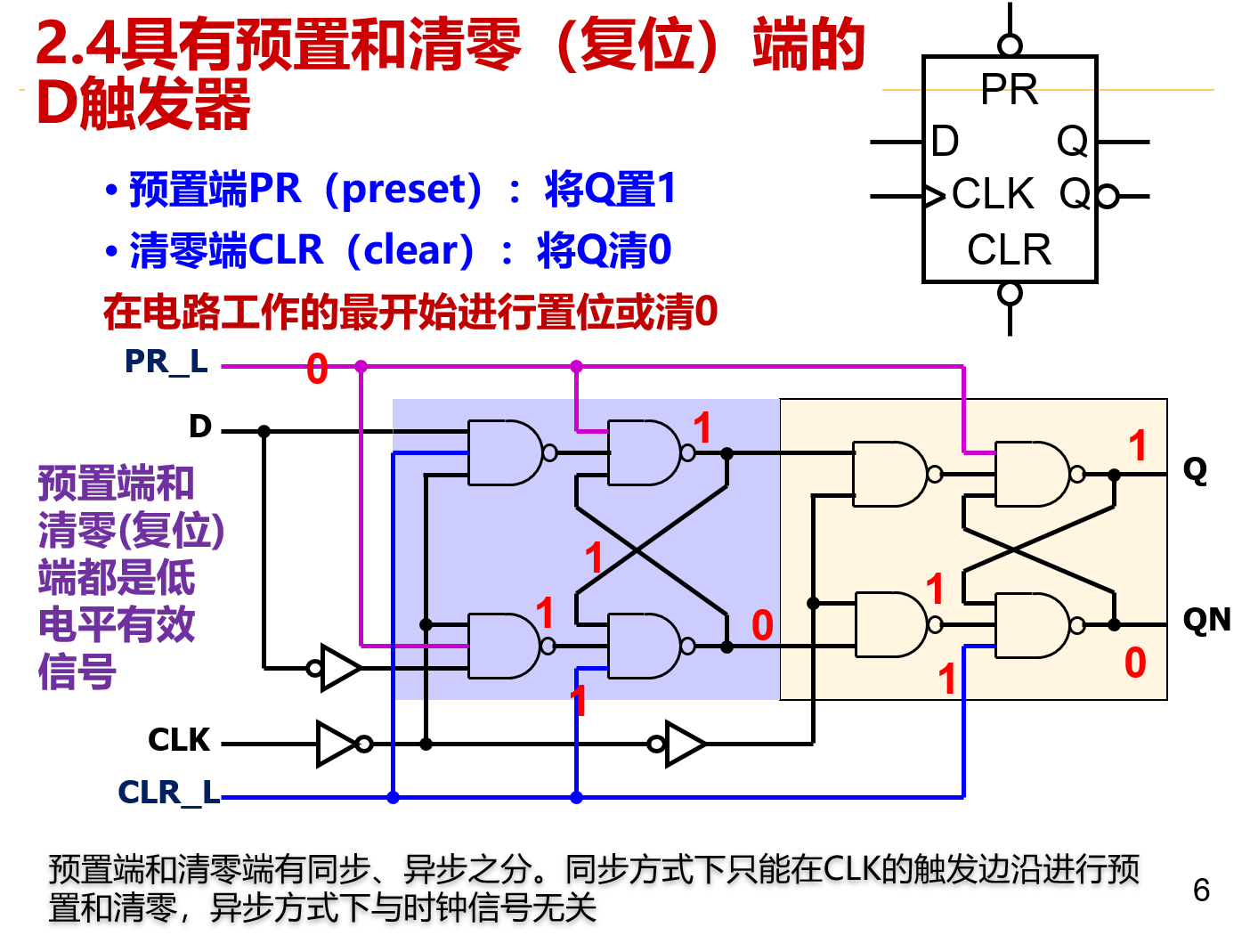

具有预制和清零(复位)端的D触发器

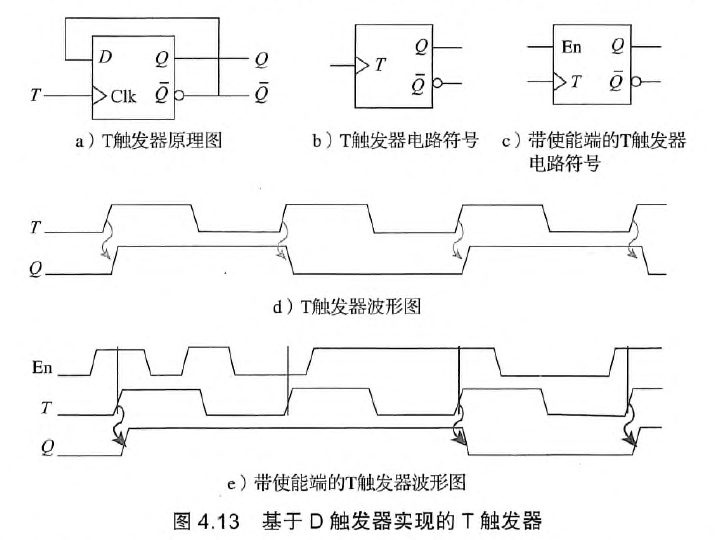

5.T触发器

- 在每个时钟脉冲T的触发边沿都会改变状态

- 基于D触发器实现,可用于实现计数器、分频器等功能

- Title: 4.2锁存器和触发器

- Author: SyEic_L

- Created at : 2025-03-17 21:55:18

- Updated at : 2025-03-21 10:15:11

- Link: https://blog.syeicl.vip/2025/03/17/4-2锁存器和触发器/

- License: This work is licensed under CC BY-NC-SA 4.0.

推荐阅读

Comments