4.4典型时序逻辑部件设计

1.计数器

- 一般从0开始计数,在达到最大计数值时输出一次计数完成信号,并重新开始计数

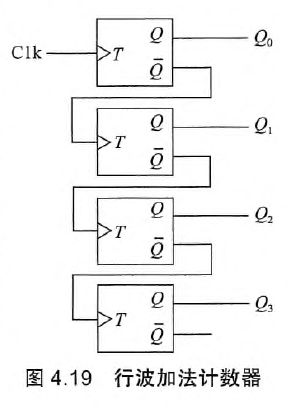

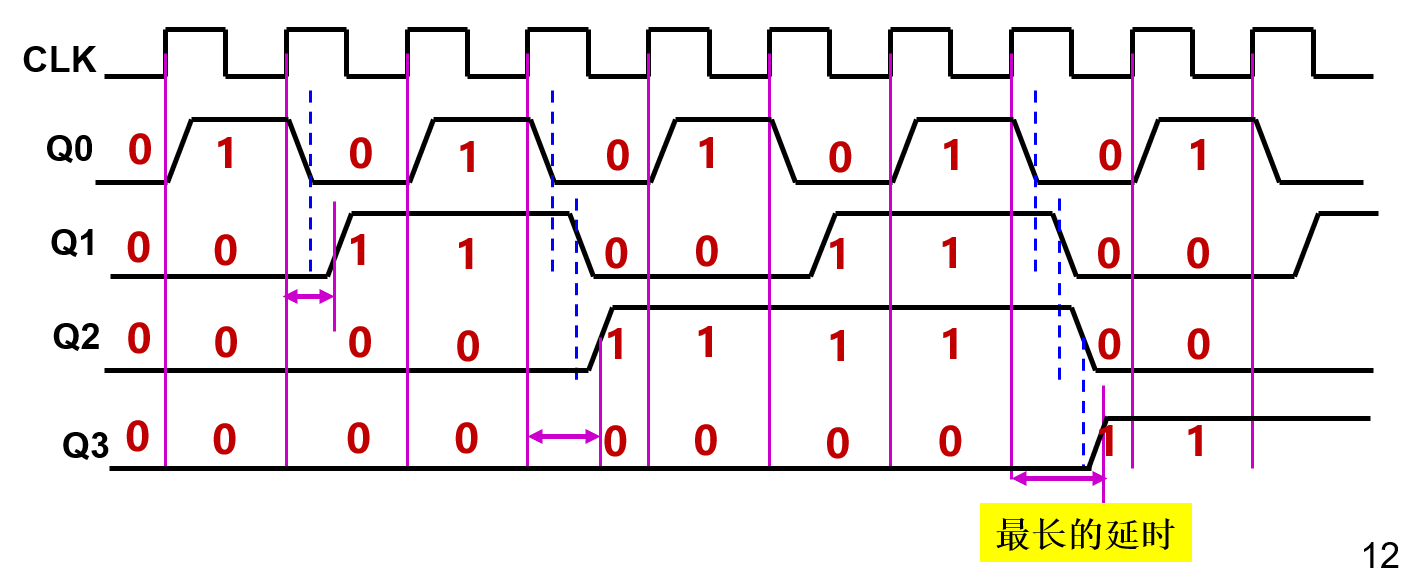

异步行波加法计数器

用T触发器实现(假设上升沿触发),激励输入串行传递,每个时钟周期传递一次。

当编码为1111时,下个时钟到达时,经过最长的延时,又回到0000

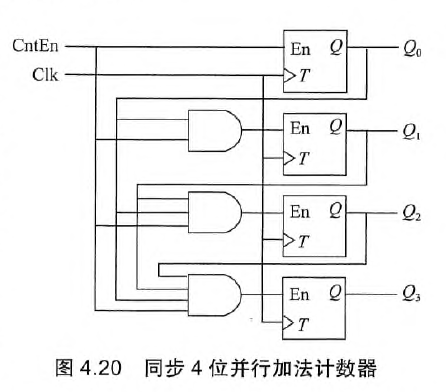

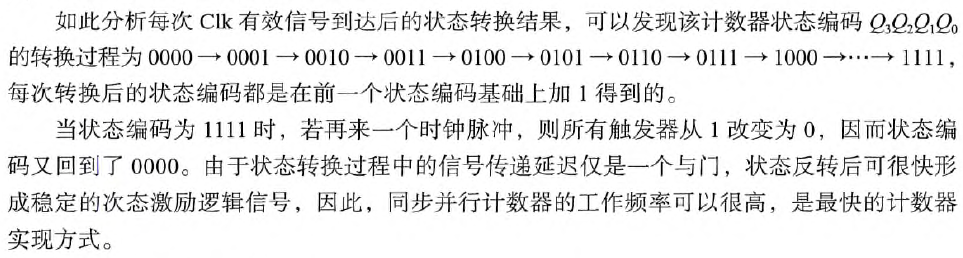

同步并行加法计数器

- 所有触发器共用同一个时钟信号

- 在时钟信号边沿到达后,所有触发器的输出同时发生变化

- 带使能端EN的T触发器,上升沿触发

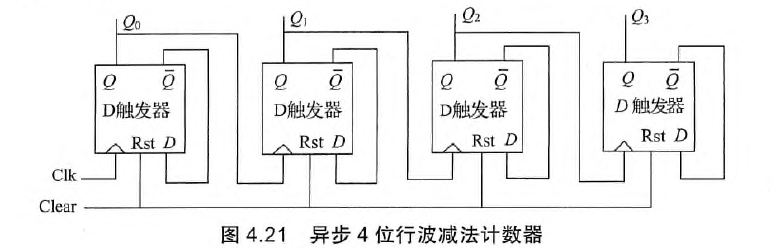

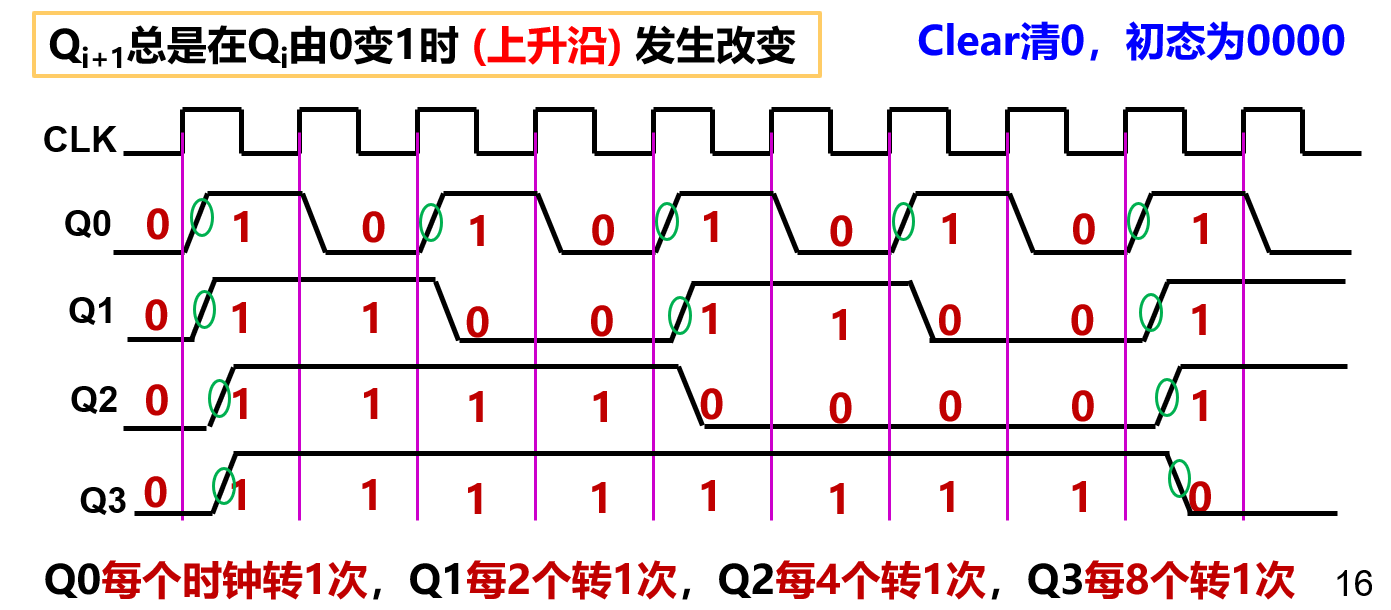

二进制异步行波减法计数器

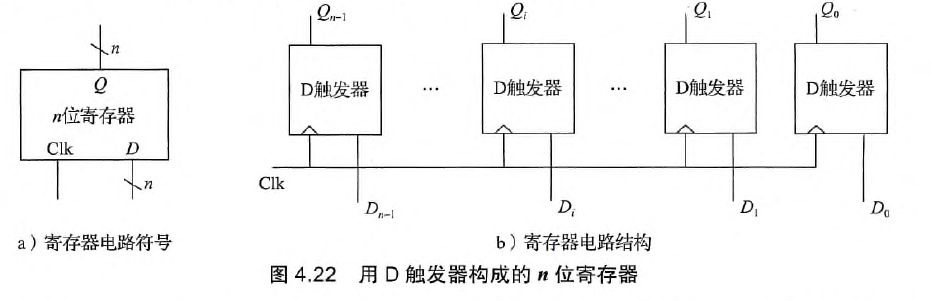

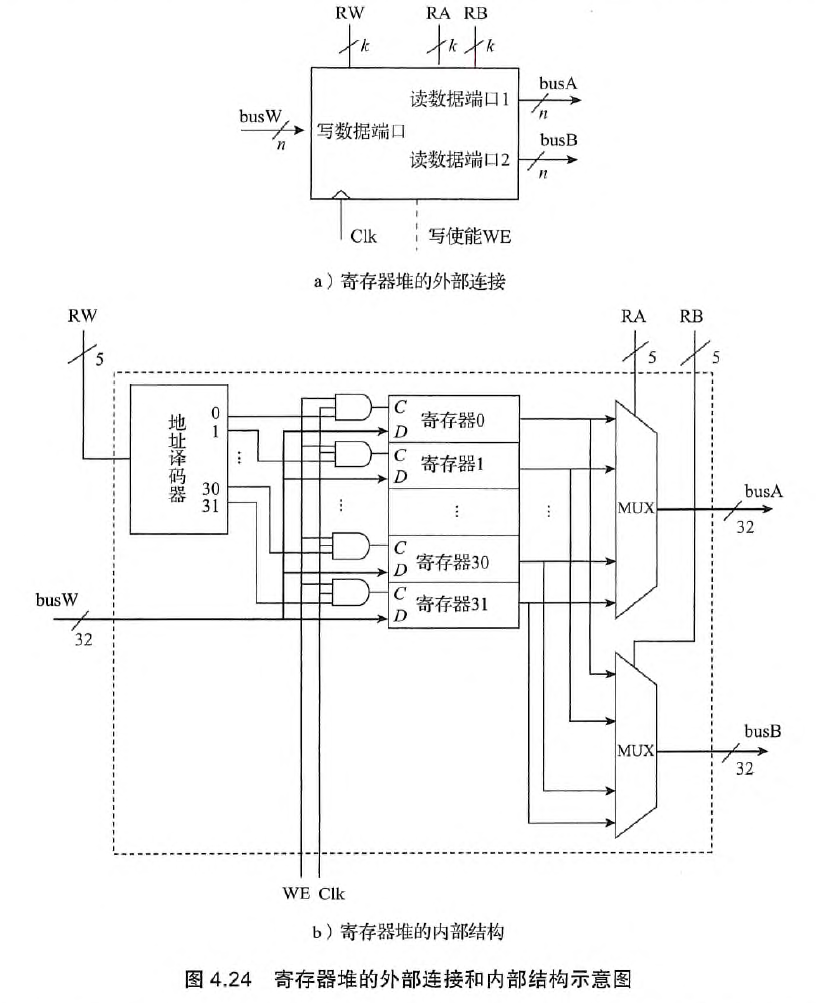

2.寄存器和寄存器堆

- 寄存器是用来暂存信息的逻辑部件

- 寄存器可直接由若干个触发器组成

- 不超过个寄存器

- 读操作属于组合逻辑操作

- 写操作属于时序逻辑操作

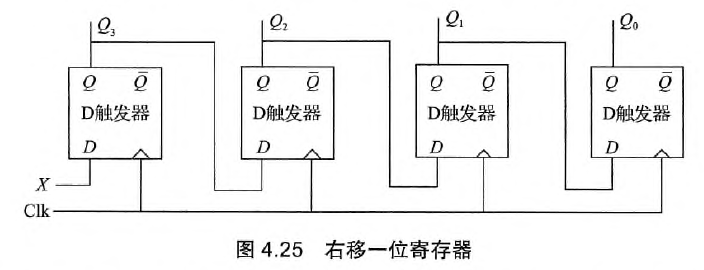

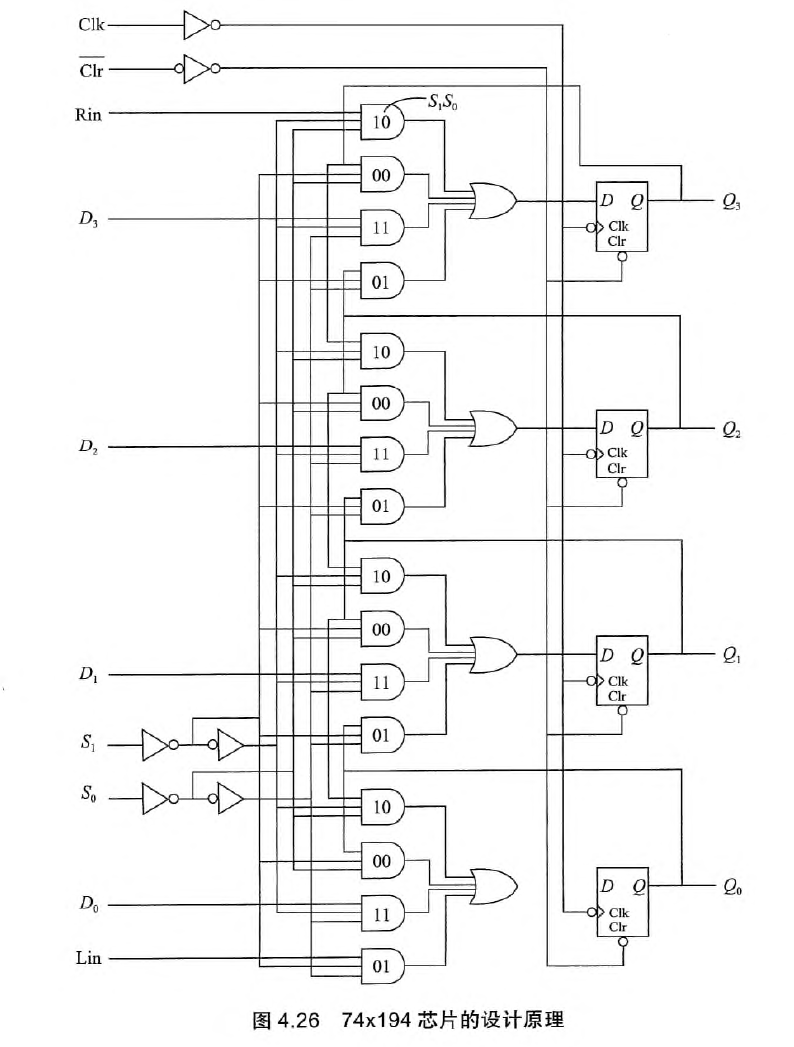

3.移位寄存器

桶形移位器

- Title: 4.4典型时序逻辑部件设计

- Author: SyEic_L

- Created at : 2025-03-23 20:32:39

- Updated at : 2025-03-24 21:51:55

- Link: https://blog.syeicl.vip/2025/03/23/4-4典型时序逻辑部件设计/

- License: This work is licensed under CC BY-NC-SA 4.0.

推荐阅读

Comments