7.3指令系统实例:RISC-V架构

1.RISC-V指令系统概述

核心:RV32I

扩展标准集:RV32M、RV32F、RV32D、RV32A

32位架构RV32G = RV32IMAFD

压缩指令集RV32C(指令长度16位)

32位架构RV64G = RV64MAFD

压缩指令集RV64C(指令长度16位)

2.RISC-V指令参考卡

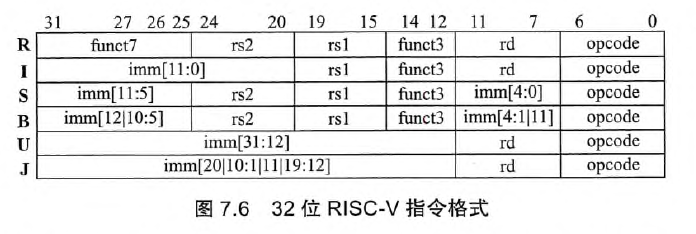

R-型为寄存器操作数指令

I-型为短立即数或装入(Load)指令

S-型为存储(Store)指令

B-型为条件跳转指令

U-型为长立即数操作指令

J-型为无条件跳转指令

opcode:7位操作码字段

rd、rs1和rs2:通用寄存器编号

imm:立即数,其位数在括号[]中表示

funct3和funct7:分别表示3位功能码和7位功能码,和opcode字段一起定义指令的操作功能

3.基础整数指令集

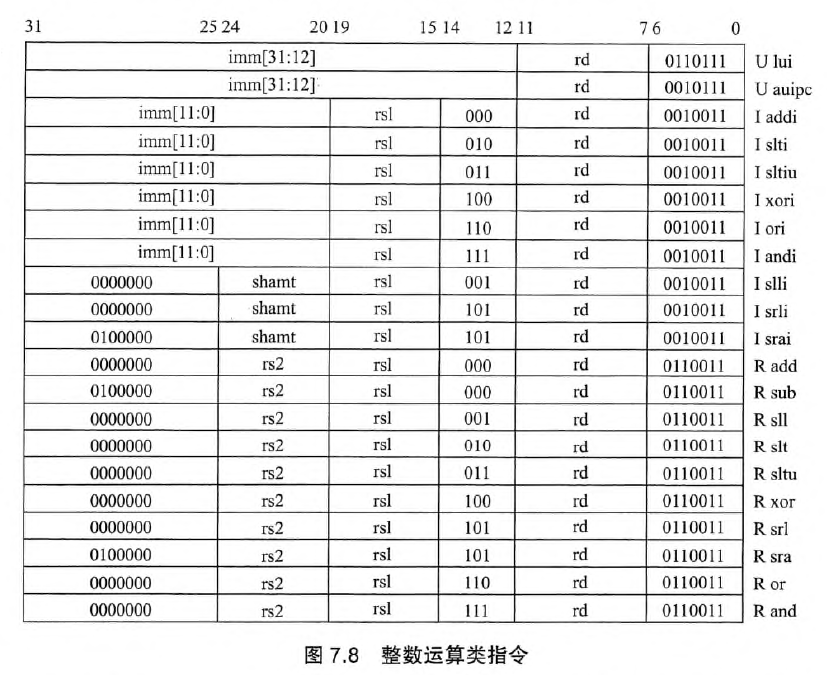

整数运算

- lui rd, imm20:将立即数imm20存到rd寄存器高20位,低12位为0。

- sltiu rd, rs1, imm12:将rs1内容与imm12符号扩展结果按无符号整数比较,若小于,则1存入rd中;否则,0存入rd中。

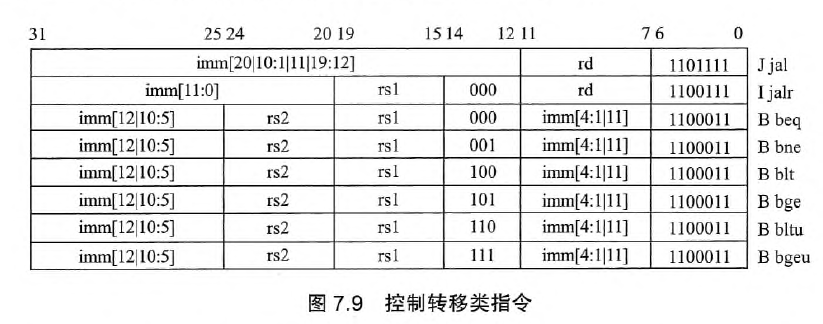

控制转移

- jal:PC←PC+SEXT[imm[20:1]<<1];R[rd]←PC+4

jal x1, imm:实现过程调用

jal x0, imm:实现无条件跳转 - jalr:PC←R[rs1]+SEXT[imm[12]];R[rd]←PC+4

jalr x0, x1, 0:实现过程调用的返回 - B型:分支指令,判断后转移

转移目标地址:PC+SEXT[imm[12:1]<<1]

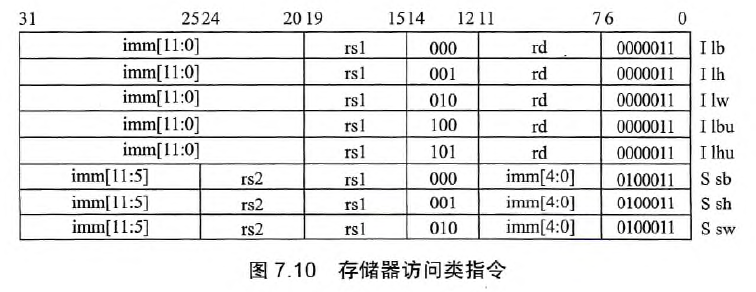

存储访问

- I型:取数指令:R[rd] ← M[R[rs1] + SEXT[imm12]]

Ibu、Ihu:分别为无符号字节、半字取,取出数据按0扩展为32位,装入rd - S型:存数指令:M[R[rs1] + SEXT[imm12]] ← R[rs2]

sb、sh:分别将rs2寄存器中低8、低16位写入存储单元中 - 汇编形式:lw rd, imm12(rs1)

sw rs2, imm12(rs1)

4.可选扩展指令集

- Title: 7.3指令系统实例:RISC-V架构

- Author: SyEic_L

- Created at : 2025-04-21 16:00:14

- Updated at : 2025-04-21 16:00:14

- Link: https://blog.syeicl.vip/2025/04/21/7-3指令系统实例:RISC-V架构/

- License: This work is licensed under CC BY-NC-SA 4.0.

推荐阅读

Comments