8.1CPU概述

1.CPU的基本功能

2.CPU的基本组成

- 数据通路—指令的执行部件

- 操作元件(ALU)

- 存储元件—寄存器

- 控制器—指令的控制部件

- 译码部件

- 控制信号生成部件

- 存储元件—寄存器

数据通路

- 两类元件组成

- 组合逻辑元件

- 时序逻辑元件

- 元件间的连接方式

- 总线连接方式

- 分散连接方式

- 具体工作

- 进行数据存储、处理、传送

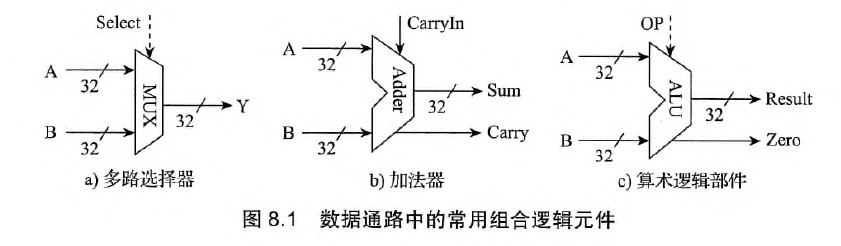

操作元件:组合逻辑电路

- 加法器

- 多路选择器

- 算逻部件(ALU)

- 译码器

状态元件:时序逻辑电路

特点

- 具有存储功能,在时钟控制下输入被写到电路中,直到下个时钟到达

- 输入端状态由时钟决定何时被写入,输出端状态随时可以读出

定时方式

- 边沿触发

最简单的状态单元

- D触发器

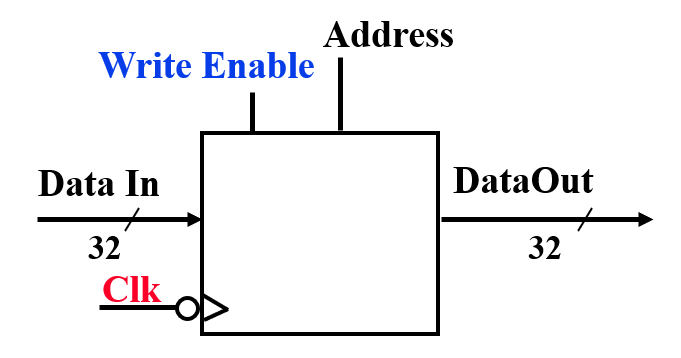

存储元件

寄存器

寄存器组

理想存储器

- Data Out:32位读出数据

- Data In:32位写入数据

- Address:读写公用一个32位地址

- 读操作(组合逻辑操作)

- 写操作(时序逻辑操作)

3.数据通路与时序控制

同步系统

- 所有动作有专门时序信号来定时

- 有时序信号规定何时发出什么动作

时序信号

- 用于进行同步控制的定时信号——时钟信号

指令周期

- CPU取并执行一条指令的时间

- 每条指令的指令周期不一样

4.计算机性能与CPU时间

- 计算机有两种不同的性能

- Time to do the task

- 响应时间

- 执行时间

- 等待时间或时延

- Tasks per day, hour, esc, ns.…

- 吞吐率

- 带宽

- Time to do the task

- CPU性能:用户CPU时间(执行用户程序中各条指令的总时间)

- CPU执行时间 = CPU时钟周期数 / 程序 ÷ 时钟频率

= CPU时钟周期数 / 程序 × 时钟周期

= 指令条数 / 程序 × CPI × 时钟周期 (Cycles Per Instruction) - 对某一条特定的指令,CPI是一个确定值——与CPU设计有关

- MIPS(定点指令执行速度)

- FLOPS

- CPU执行时间 = CPU时钟周期数 / 程序 ÷ 时钟频率

- Title: 8.1CPU概述

- Author: SyEic_L

- Created at : 2025-04-27 09:07:27

- Updated at : 2025-04-27 09:07:27

- Link: https://blog.syeicl.vip/2025/04/27/8-1CPU概述/

- License: This work is licensed under CC BY-NC-SA 4.0.

推荐阅读

Comments