8.2单周期CPU设计

设计处理器步骤

ISA确定后,进行处理器设计的大致步骤

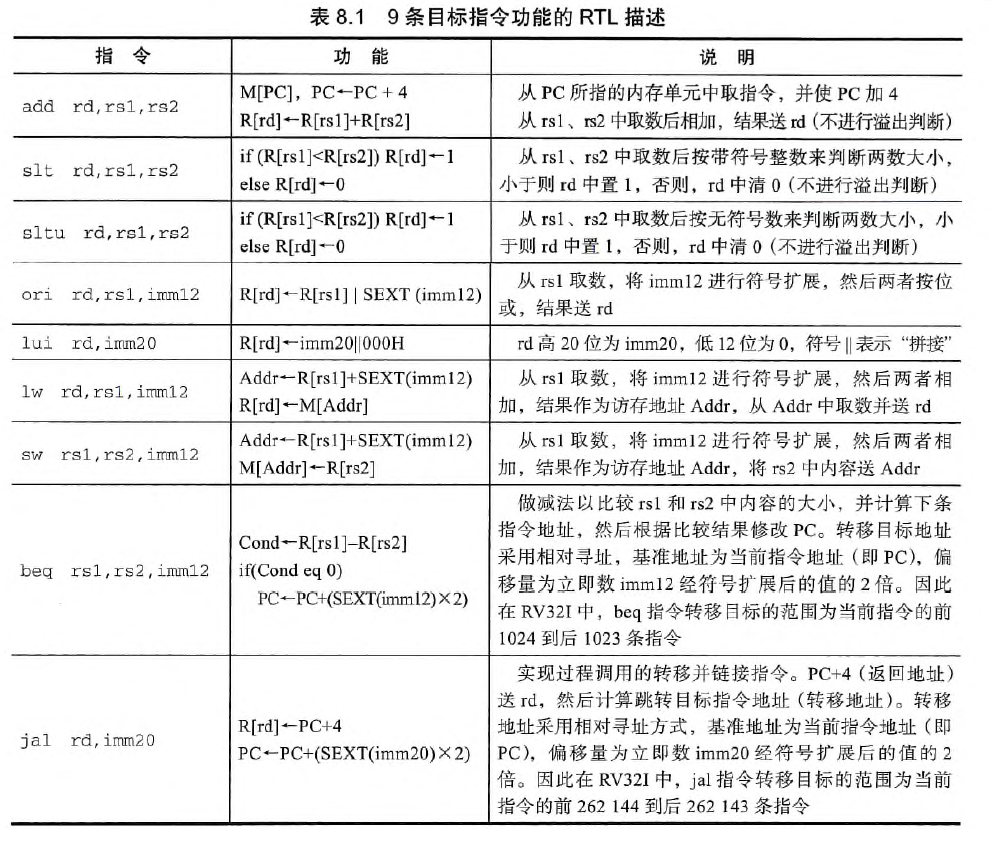

- 分析每条指令的功能,并用RTL(Register Transfer Language)来表示

- 根据指令的功能给出所需元件,并考虑如何将他们互连

- 确定每个与元件所需控制信号的取值

- 汇总所有指令所涉及到的控制信号,生成一张反映指令与控制信号之间关系的表

- 根据表得到每个控制信号的逻辑表达式,据此设计控制器电路

1.指令功能的描述

数据指定

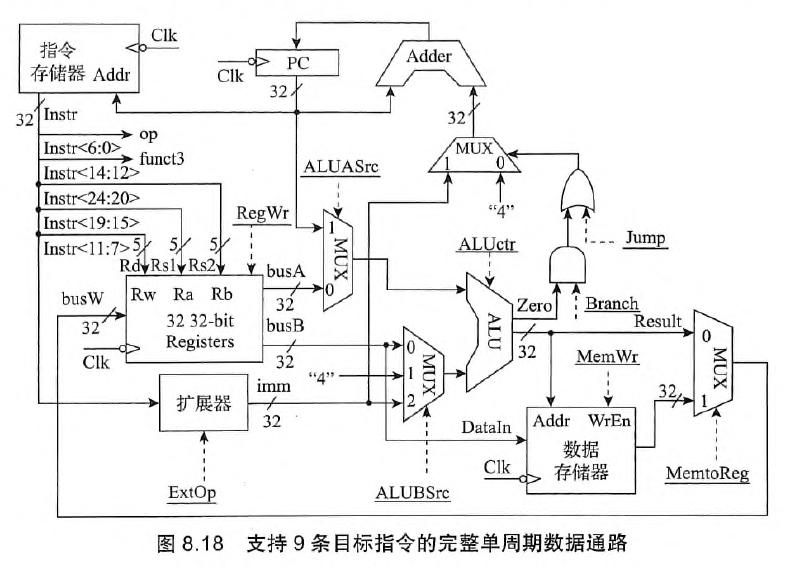

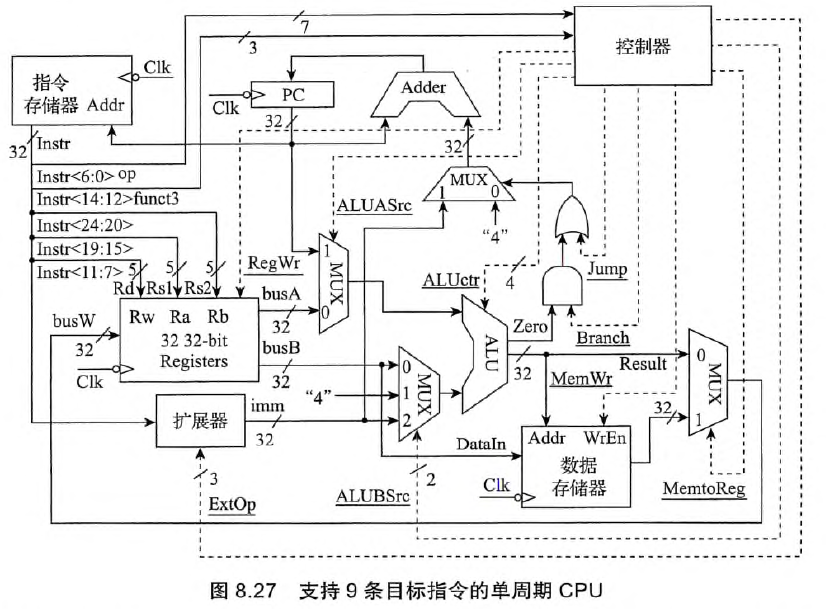

2.单周期数据通路的设计

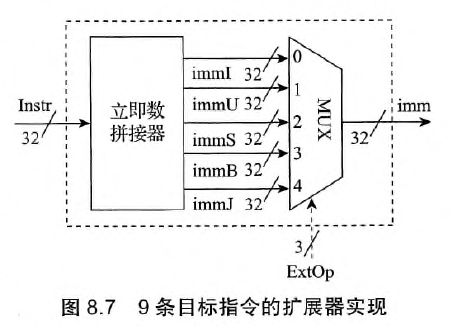

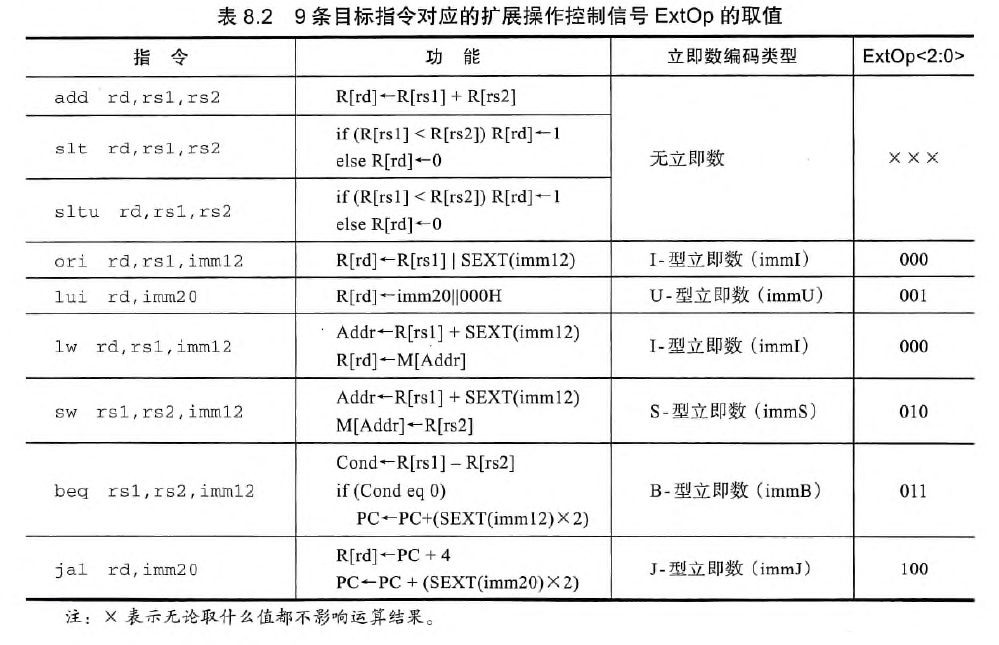

1.扩展器部件

- ExtOp(3位):扩展操作码控制

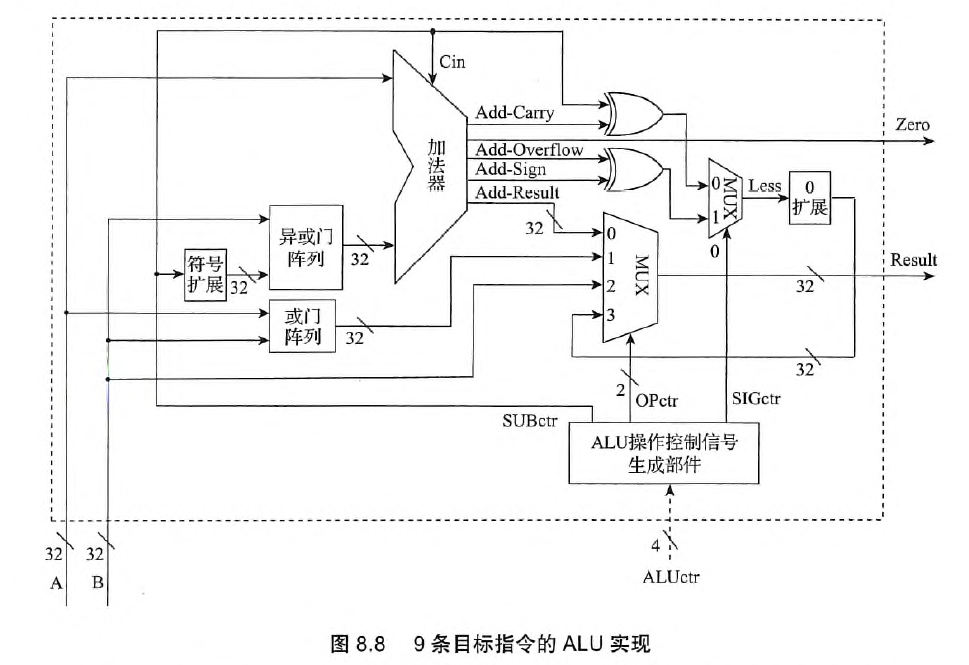

2.算术逻辑部件

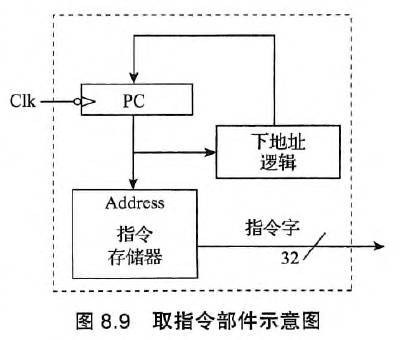

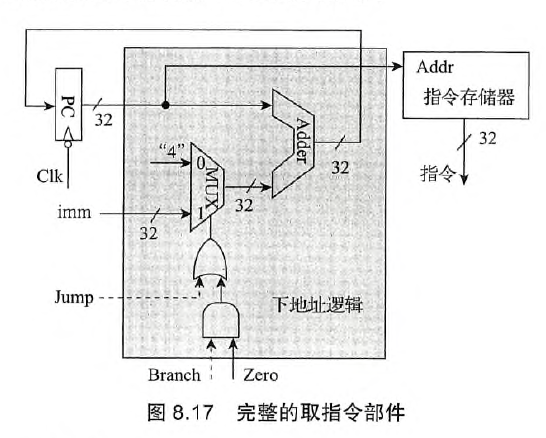

3.取指令部件

- 每条指令都有的公共操作

- 取指令:M[PC]

- 更新PC:PC←PC + 4

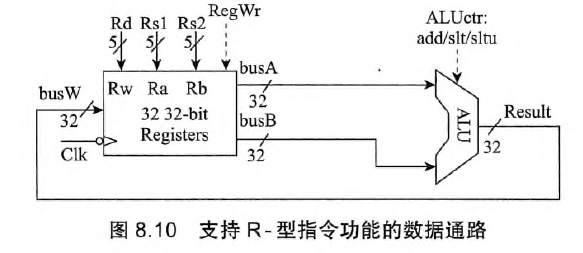

4.R-型指令的数据通路

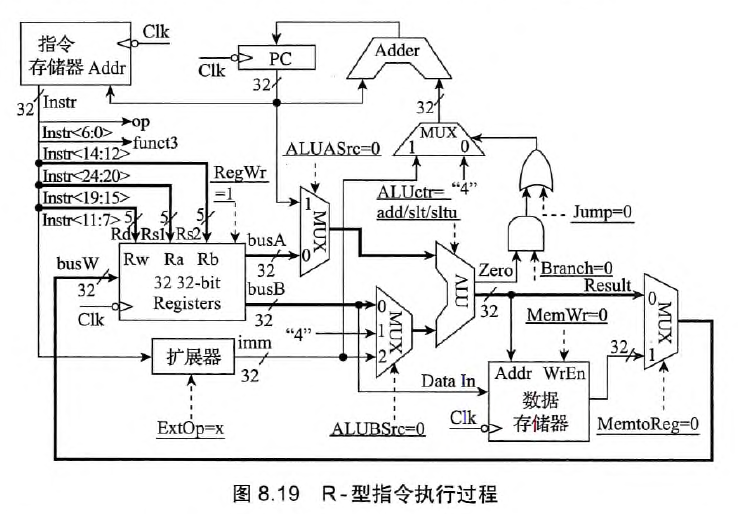

- 3条R-型指令:add、slt、sltu,都要写结果,对应的控制信号RegWr=1

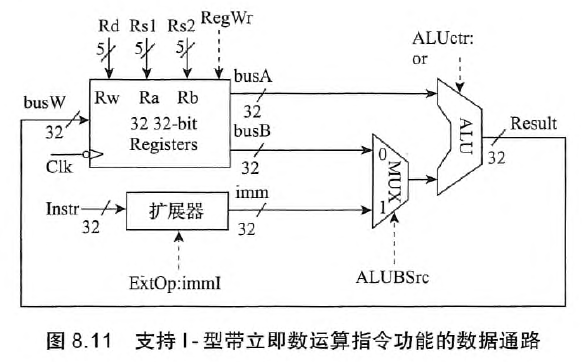

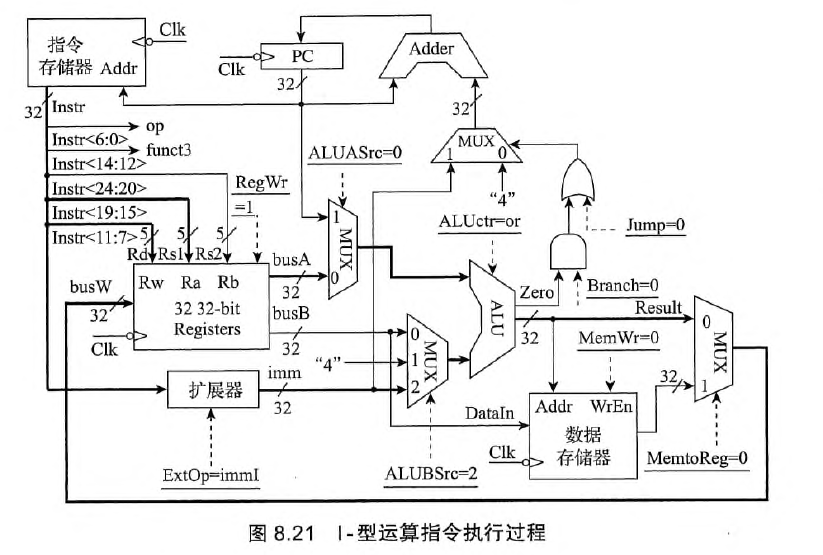

5.I-型指令的数据通路

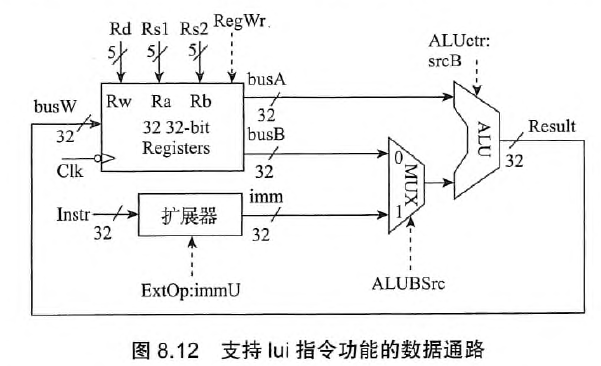

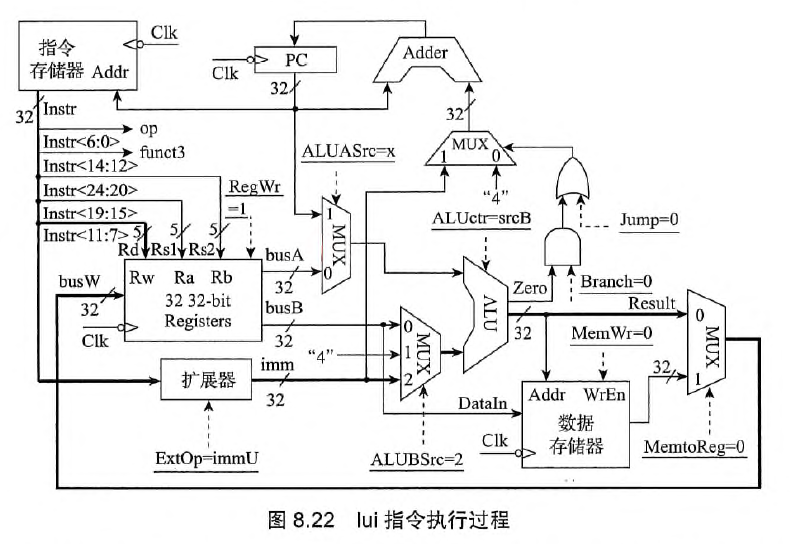

6.U-型指令的数据通路

- lui功能:R[rd]←imm20||000H 即直接将扩展器结果输出

- auipc功能:R[rd]←PC + imm20||000H 即直接将扩展器结果输出

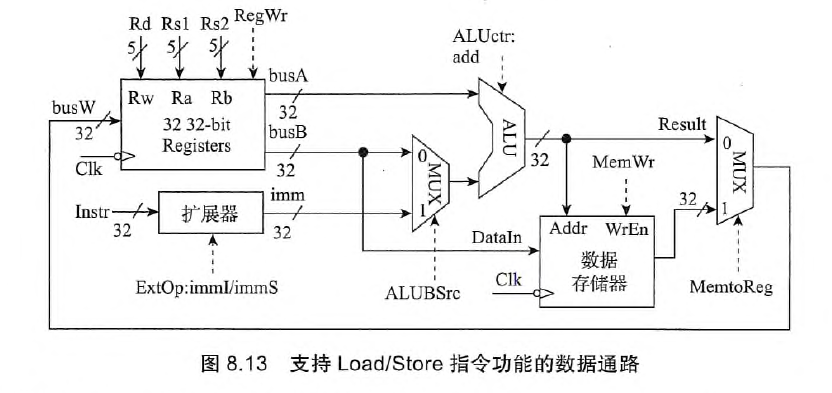

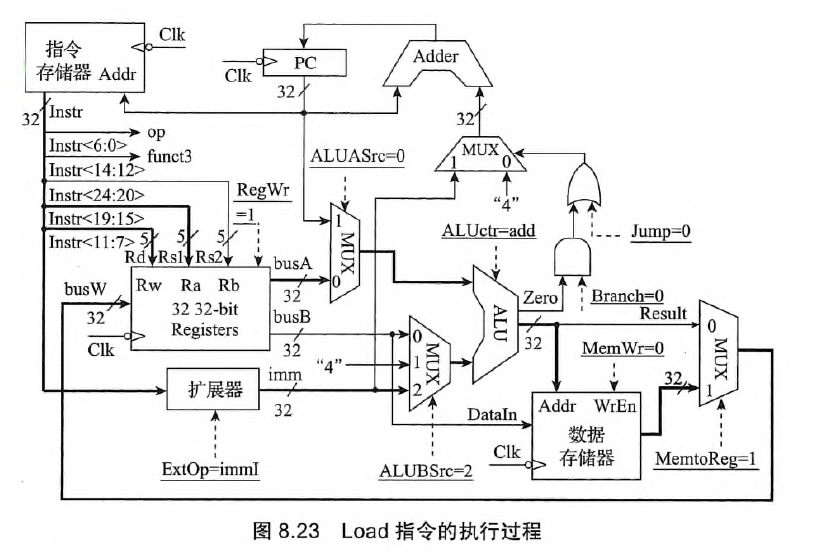

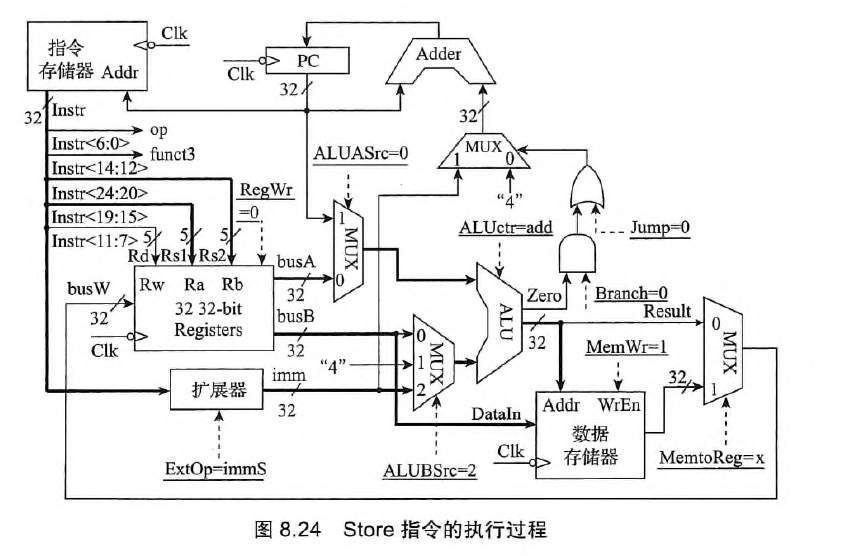

7.Load/Store指令的数据通路

- lw指令功能:R[rd]←M[R[rs1] + SEXT(imm12)]

- MemWr = 0

- MemtoReg = 1

- sw指令功能:M[R[rs1] + SEXT(imm12)]←R[rs2]

- MemWr = 1

- MemtoReg任意

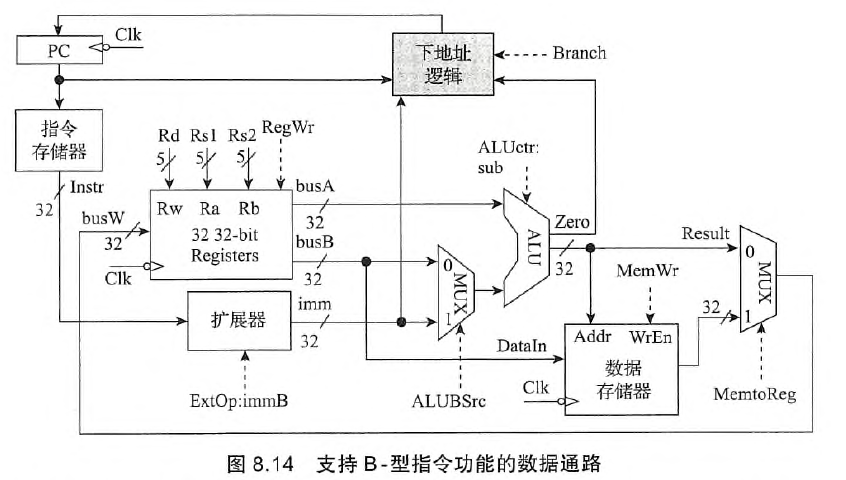

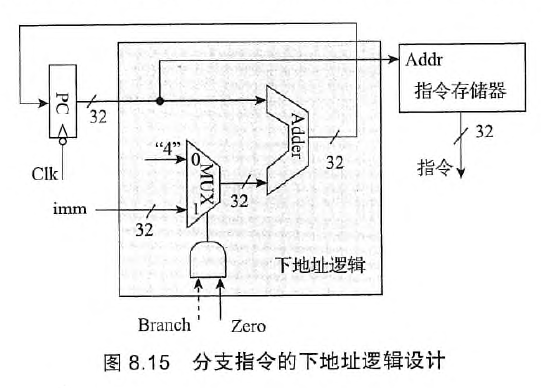

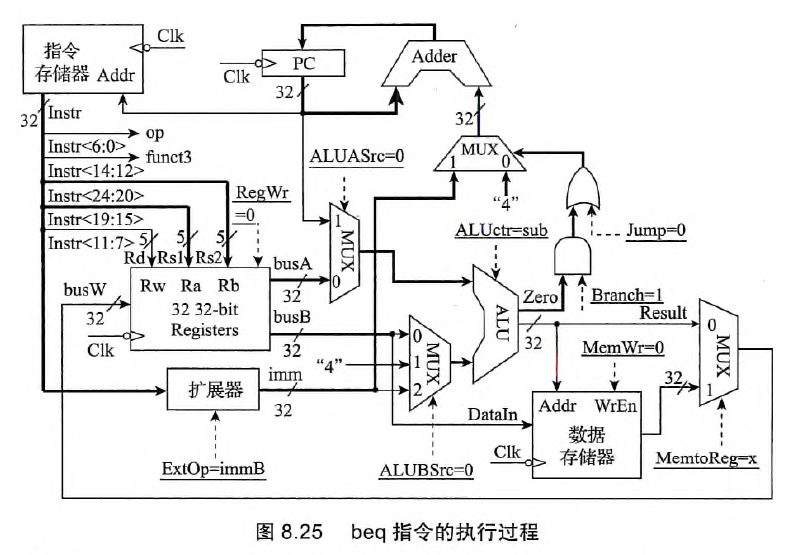

8.B-型指令的数据通路

beq指令功能:if (R[rs1] = R[rs2]) PC←PC + (SEXT(imm12) × 2) else PC←PC+4

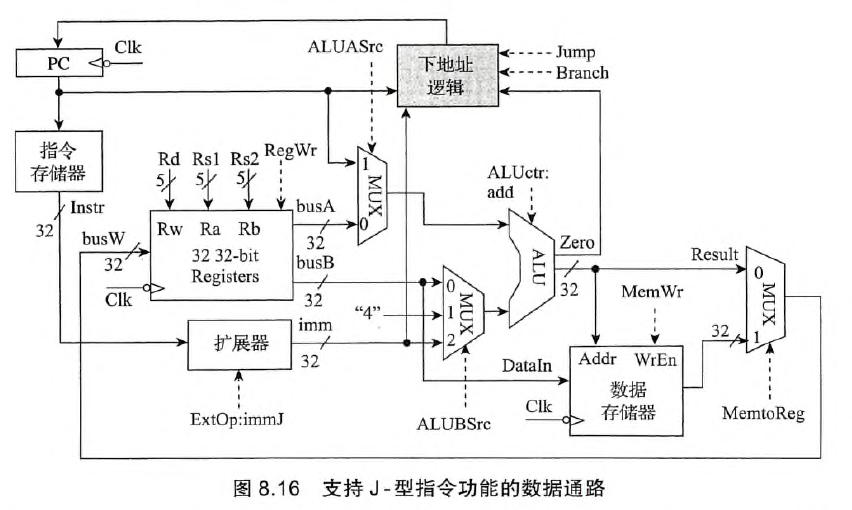

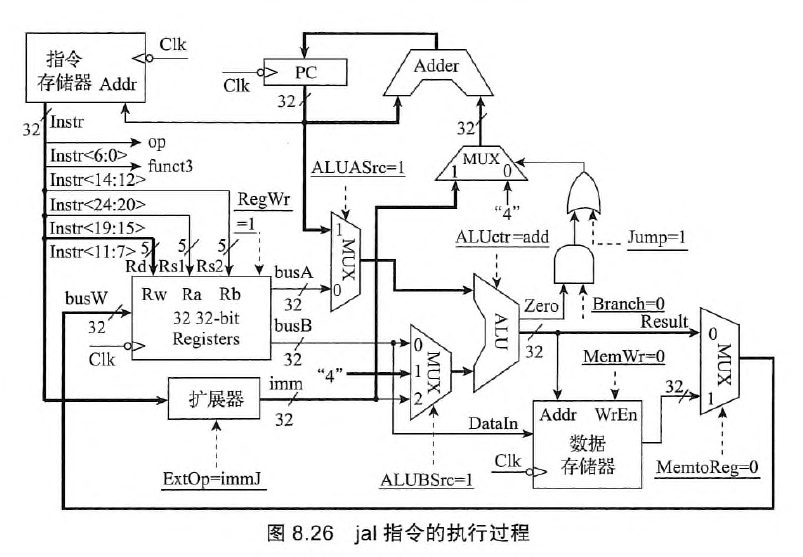

9.J-型指令的数据通路

jal指令功能:PC←PC + SEXT(imm[20:1]<<1); R[rd]←PC+ 4

10.综合9条指令的完整数据通路

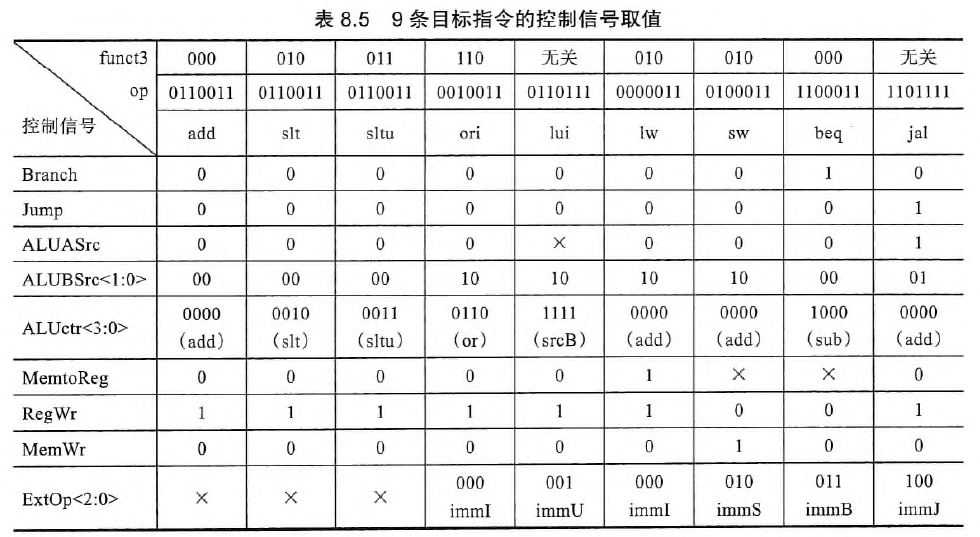

3.控制器的设计

1.控制信号取值分析

(1)R-型指令执行阶段

(2)I-型运算指令执行阶段

(3)lui指令执行阶段

(4)Load/Store指令执行阶段

(5)B-型指令执行阶段

(6)J-型指令执行阶段

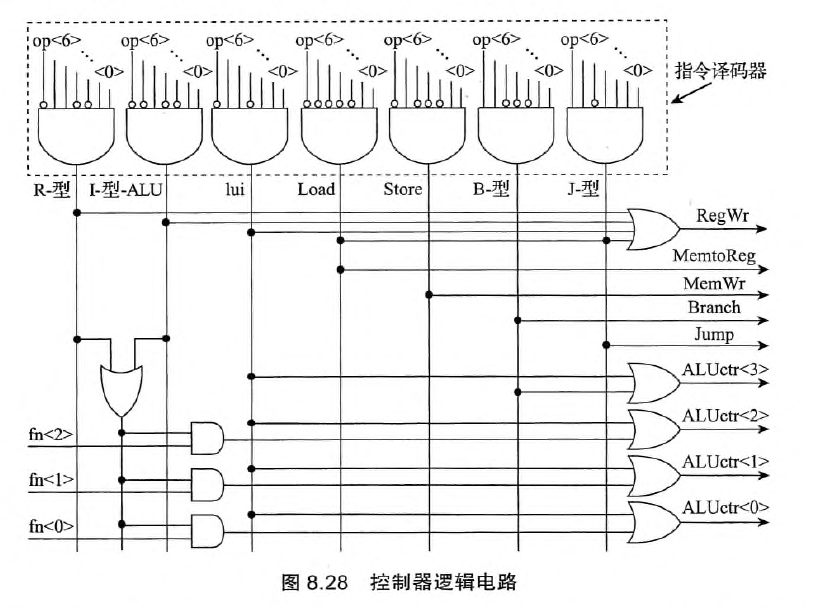

2.控制器设计

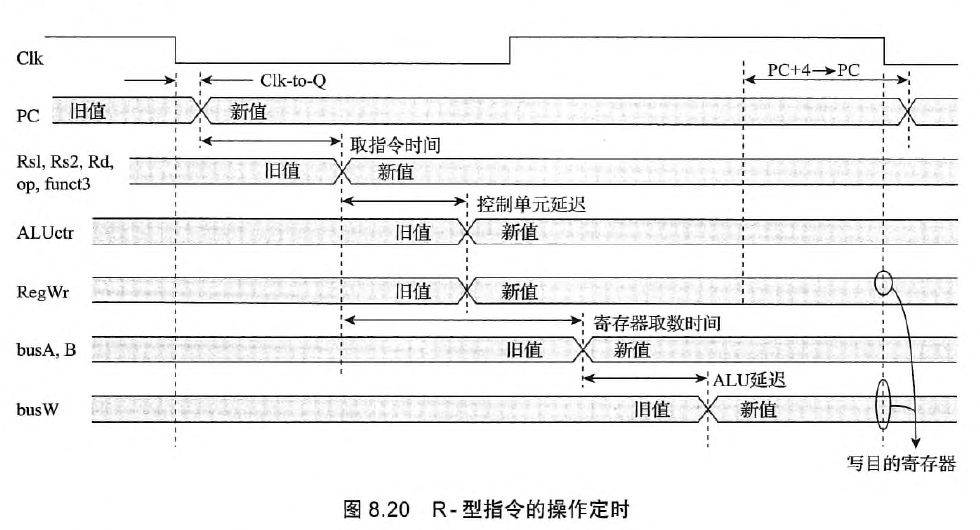

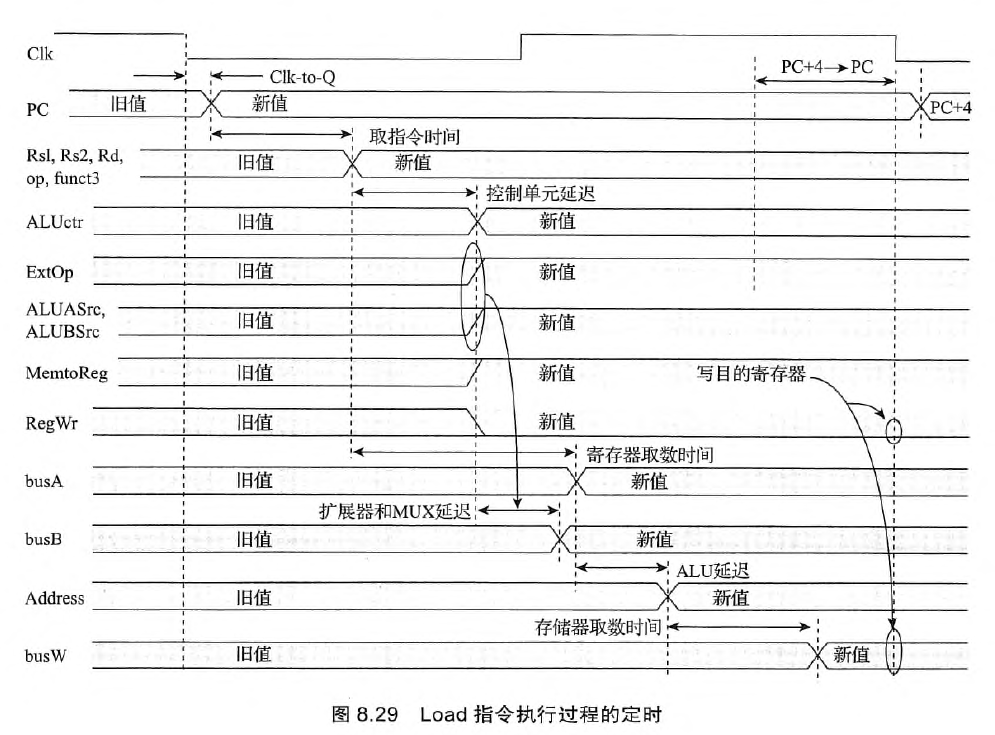

4.时钟周期的确定

- Title: 8.2单周期CPU设计

- Author: SyEic_L

- Created at : 2025-05-15 22:57:46

- Updated at : 2025-05-15 22:57:46

- Link: https://blog.syeicl.vip/2025/05/15/8-2单周期CPU设计/

- License: This work is licensed under CC BY-NC-SA 4.0.

Comments