8.3多周期CPU设计

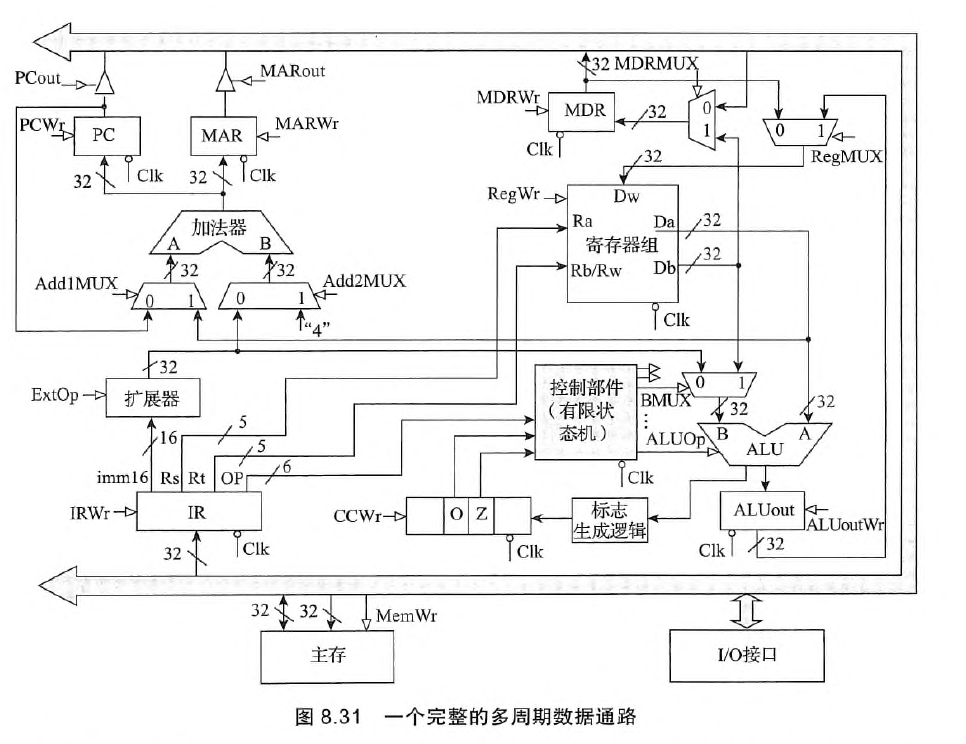

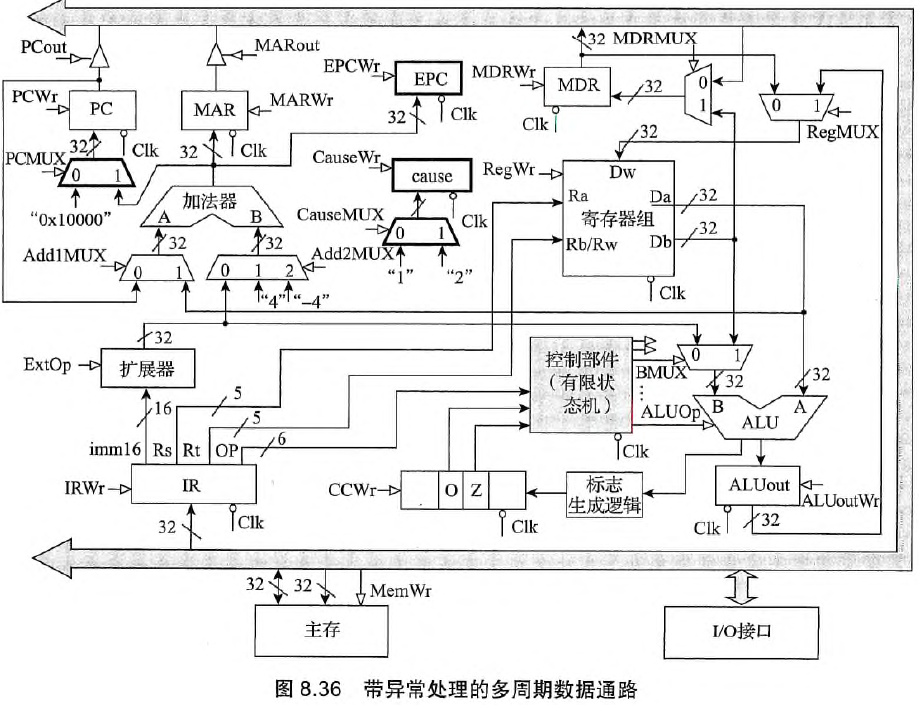

1.多周期数据通路的设计

- 分阶段

- 取指令阶段

- 执行一次存储器读操作

- 读出的内容保存到寄存器IR(指令寄存器)中

- IR的内容不是每个始终都更新,所以IR必须加一个“写使能”控制

- 在取指令阶段结束时,ALU输出为PC+4,并送到PC的输入端,但不能在每个时钟到来时就更新PC,所以PC也要有“写使能”控制

- 译码/读寄存器堆阶段

- 经过控制逻辑延迟后,控制信号更新为新值

- 执行一次寄存器读操作,并同时进行译码

- 期间ALU空闲,可以考虑“投机计算”地址

- ALU运算阶段

- ALU运算,输出结果一定要在下个始终到达之前稳定

- 读写存储器阶段(仅针对load和store)

- 由ALU运算结果作为地址访问存储器,读出或写入数据

- 写结果到寄存器

- 把之前的运算结果或读存储器结果写到寄存器堆中

- 取指令阶段

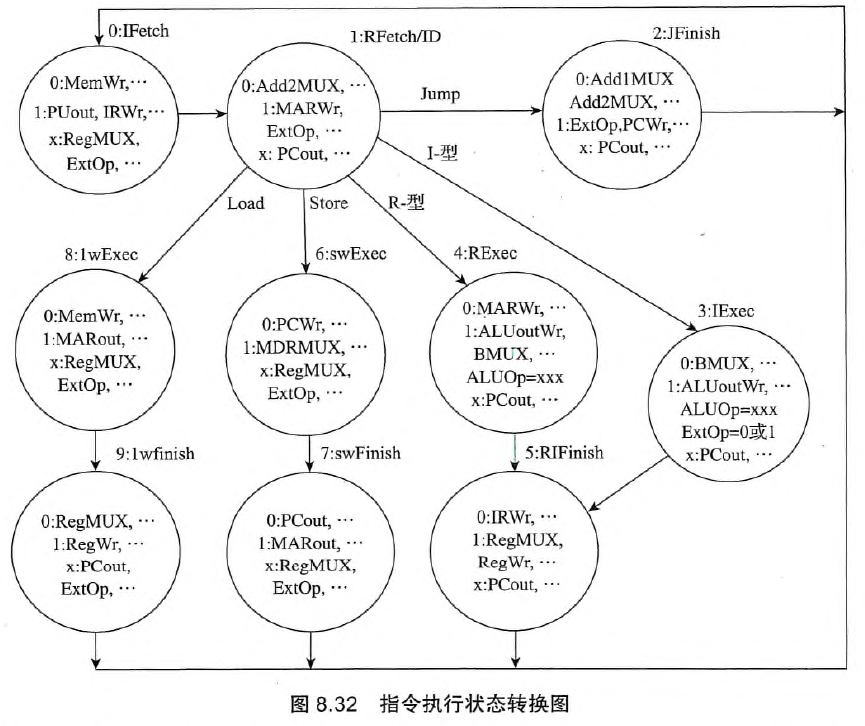

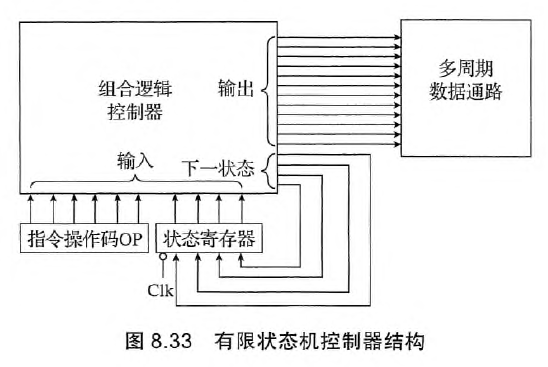

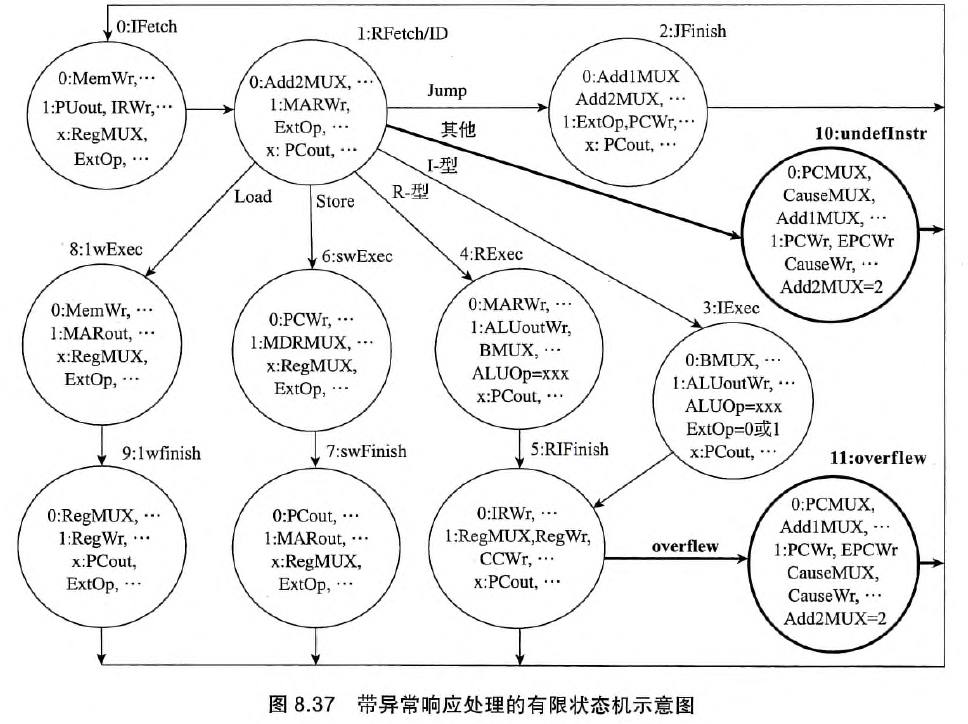

2. 硬连线控制器设计

有限状态机(PLA)

也称为组合逻辑控制器或PLA控制器或硬连线控制器

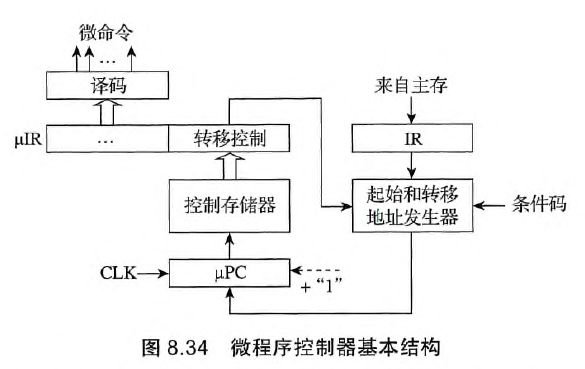

3.微程序控制器设计

- 仿照程序设计的方法,编制每个指令对应的微程序

- 每个微程序由若干条微指令构成,分别和各状态对应

- 每条微指令包含若干条微命令,分别和状态中的控制信号对应

- 所有微程序放在只读存储器中(称为控制存储器Control Storage, CS)

4.带异常处理的CPU设计

- Title: 8.3多周期CPU设计

- Author: SyEic_L

- Created at : 2025-05-31 16:22:39

- Updated at : 2025-05-31 16:22:39

- Link: https://blog.syeicl.vip/2025/05/31/8-3多周期CPU设计-1/

- License: This work is licensed under CC BY-NC-SA 4.0.

推荐阅读

Comments