3.1组合逻辑电路概述

1.组合逻辑电路构成规则

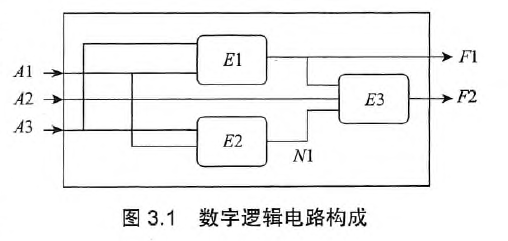

数字逻辑电路可以看成带有若干输入端和若干输出端的黑盒

内部可看成若干元件和若干节点

元件本身又可以是一个数字逻辑电路

节点可以是输入结点(A1)、内部结点(N1)、输出结点(F1)

组合逻辑电路

- 输出值仅依赖于当前输入值

时序逻辑电路

- 不仅依赖输入值,还与当前状态有关

- 电路中存在存储部件或反馈结构

最简单的组合逻辑电路是逻辑门电路

构成规则

- 每个原件本身是组合逻辑电路

- 输出结点不能互联

- 输出结点不能反馈到输入端

2.逻辑电路图

描述数字电路内部元件的结构及其相互连接关系

每个逻辑电路图对应一个逻辑表达式(多个输入,一个输出)

一个真值表可能对应多个不同的逻辑表达式,从而对应多个不同的逻辑电路图,因而可以有多个不同的实现方式

扇入系数:一个逻辑门所允许的输入端的最大数目

扇出系数:一个逻辑门输出端信号所能驱动的下一级输入段的最大数目

优先级

非 > 与和与非 > 异或和同或 > 或和或非

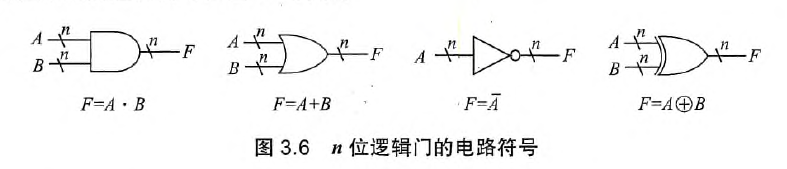

n位二进制运算在输入端和输出端标注位数即可

3.两级和多级组合逻辑电路

- 门延迟:信号通过逻辑门在时间上存在延迟,从输入信号改变开始,到输出信号发生改变所用的时间

- 任何逻辑表达式都可以转换成与-或表达式和或-与表达式,因此,任何组合逻辑电路都可以是一个二级电路

- 两级组合逻辑电路可能会使所需的硬件数量会成倍增长

- 采用两级还是多级需要在速度和成本之间进行权衡

4.组合逻辑电路设计

无关项

某些输入组合对应的输出值可以是任意值,某些输入组合不可能出现

这些输入组合对应的输出值在化简时标识为d,表示可以取值0或1

例如,8421BCD码,大于1001的编码为无关项

5.非法值和高阻态

非法值

- 信号不能被识别为高或低,处于不确定状态

高阻态

输出处于非正常逻辑态的第三种电气态,好像和电路断开一样(对下一级电路无影响)

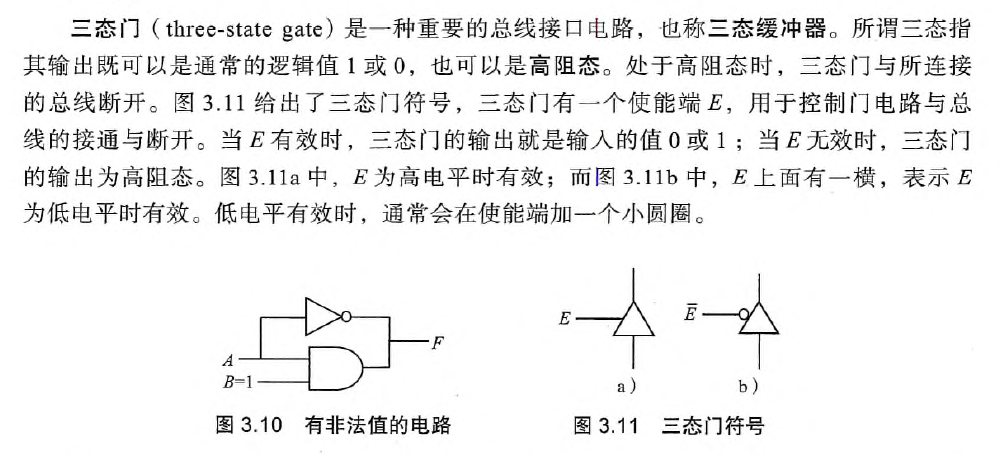

三态门

- 三态缓冲器,输出值既可以是1或0,又可以是高阻态

- 有一个额外的输出使能控制端EN

- Title: 3.1组合逻辑电路概述

- Author: SyEic_L

- Created at : 2025-03-07 20:34:07

- Updated at : 2025-03-10 17:22:30

- Link: https://blog.syeicl.vip/2025/03/07/3-1组合逻辑电路概述/

- License: This work is licensed under CC BY-NC-SA 4.0.

Comments